[科普]小型化的微波产品工艺知识

[科普]小型化的微波产品工艺知识

一.小型化微波产品射频电路的典型结构型式

随着军事工业产品的发展,对于微波产品要求小型化、高可靠性与稳定性的要求,微波产品传统结构已不能满足要求;国外在80年代开始发展薄膜技术、微组装技术以及相关的材料应用,使产品小型化完全能够实现,已在国内外进入大量工业应用阶段,其典型的产品结构如下:裸装芯片和薄膜电路、LTCC电路共晶焊在载板上,载板共晶焊在铝或铜盒体上,热匹配原因载板材料通常采用可瓦合金、钨铜合金、钼铜合金;为了更高的可靠性,可以采用激光封焊技术对产品盒体进行整体封装。该结构产品有很明显优势,体积为传统结构十分之一属于常态、整体材料系导热性良好、电路及互连线均为纯金,所以小型化、高温可靠性、长期稳定性和产品一致性得以保证。

| 传统结构及工艺 | 混合结构及工艺 | 小型化的结构及工艺 | |

| 射频电路 | 聚四氟乙烯薄铜板、ROGERS的陶瓷粉填充聚四氟乙烯薄铜板、 | 聚四氟乙烯薄铜板、ROGERS的陶瓷粉填充聚四氟乙烯薄铜板、 | 薄膜电路制作射频电路; |

| ROGERS的陶瓷粉热固性树脂薄铜板等印制电路 | ROGERS的陶瓷粉热固性树脂薄铜板等印制电路 | LTCC制作频率部分射频电路和控制电路。 | |

| 厚膜电路制做部分高频电路; | |||

| 功能芯片 | 封装型式 | 封装或裸芯片 | 裸芯片 |

| 功能电路及芯片固定 | 机械连接、锡焊、导电胶 | 机械连接、锡焊、导电胶 | 金锡、金锗共晶焊;导电胶 |

| 器件互连 | 铜线焊接 | 铜线焊接、金线焊接(AU Wire bonding)、金带焊接((AU Ribbon Welding) | 金线焊接(AU Wire bonding)、金带焊接((AU Ribbon Welding) |

| 系统热稳定 | 一般 | 较好 | 好 |

| 产品体积 | 大 | 大 | 小 |

| 稳定性 | 一般 | 较好 | 很好 |

二.薄膜电路(Thin-Fi lm Circuits)

1 产品特性

薄膜电路是在沉积不同金属膜的绝缘基片上,通过精密光刻和薄膜工艺来制成包含高性能电感、电阻和导线的电路. 将元件和其他所需器件同时放在此电路基片上,即可形成高性能和高可靠性的混合微波集成电路(HMIC)。此电路的优点是体积小、重量轻、热耗散好、高频率和宽带性能及高可靠性, 可以工作于1-40GHz直至毫米波、太赫兹波段,对于石英基材的薄膜电路可以工作于太赫兹。适用于无线通信设备的应用。

2 基板类型及材料特性

| 特性 | 抛光氧化铝(Al2O3) | 共烧氧化铝(Al2O3) | 氧化铍(BeO) | 氮化铝(AlN) | 石英(SiO2) |

| 化学成分 | Al2O3 | Al2O3 | BeO | AlN | SiO2 |

| 纯度 (%) | 99.6 | 99.6 | 99.5 | 98 | 100 |

| 密度d (g/cm3) | 3.87 | 3.87 | 2.85 | 3.28 | 2.2 |

| 热膨胀系数 (ppm/℃) | 7.0-8.3 | 7.0-8.3 | 9.0 (25-1000℃) | 4.6 | 0.65 |

| (25-1000℃) | (25-1000℃) | (25-300℃) | (25-320℃) | ||

| 热导率 (W/m·K) | 26.9 | 26.9 | 270 | 170 | 1 |

| 相对介电常数 (εr) | 9.9 | 9.9 | 6.5 | 8.6 | 3.8 |

| @25℃1MHz | @25℃1MHz | @25℃1MHz | @25℃ | @25℃1MHz | |

| 1MHz | |||||

| 损耗 (@ 1MHz) | 0.0001 | 0.0001 | 0.0004 | 0.001 | 0.000015 |

| 绝缘强度 (kV/cm) | 4000 | 4000 | --- | --- | 10000 |

| 晶粒尺寸 (μm) | <1.0 | <1.0 | 9–16 | 5–7 | Amorphous |

| 硬度 (Rockwell) | 87 | 87 | 45 | n/a | 7Mohs |

| 弯曲强度 K(10-3) lbs/in2 | 90 | 90 | 35 | 59 | 25 |

| 抗压强度 | 54 | 54 | ---- | ---- | 161 |

| M(10-3) lbs/in2 | |||||

| 基板尺寸 (inches) | 1月3日 | 1月3日 | 1-2.25 | 1-2.25 | 1-2.25 |

蓝宝石(sapphire ):相对介电常数 (εr)-11.5;损耗 (@ 1MHz)—0.00086

材料选用和频率相关,推荐如下:

<6~8GHz 0.025”厚度Al2O3

<12GHz 0.020”厚度Al2O3

<25~26GHz 0.015”厚度Al2O3

<30~32GHz 0.010”厚度Al2O3

<60~70GHz 0.005”厚度Al2O3

<70~80 GHz 0.010”厚度石英

<130~140 GHz 0.005”厚度石英

>140 GHz <0.005”厚度石英

3 薄膜电路选型

| 序号 | 项目 | 标准选用 | 备注 |

| 1 | 基片材料 | 99.6%Al2O3、石英 | |

| 2 | 基片材料厚度 | 10mil(0.25mm) | 5mil(0.127mm) |

| 15mil(0.38mm) | 或更小 | ||

| 20mil(0.51mm) | |||

| 25mil(0.63mm) | 需申请 | ||

| 3 | 基片材料厚度通用公差 | ±0.025mm | |

| ±0.05mm(大于20mil厚) | |||

| 4 | 基片表面粗糙度 | <0.1μm | |

| 5 | Au的厚度 | 正面:4μm | 其它要求需申请 |

| 背面:大于1μm | |||

| 6 | Au的厚度公差 | ±20% | |

| 7 | 最小导线宽度 | 10μm | 电镀20μm |

| 8 | 最小导线间隙 | 20μm | 电镀10μm |

| 9 | 导线宽度公差 | ±2.5μm | |

| 10 | 电阻 | 50Ω/方 | 其它需申请 |

| 11 | 电阻公差 | ±10% | 更小公差需申请 |

| 12 | 最小电阻尺寸 | 25μm | 更小尺寸需申请 |

| 13 | 导线/电阻距电路边沿最小距离 | 50μm | |

| 14 | 成品电路最小尺寸 | 0.4mm | 更小尺寸需申请 |

| 15 | 成品电路尺寸公差 | ±0.05mm | 更小公差需申请 |

几点说明

3.1 基板材料

99.6%Al2O3:根据美国的使用,95%以上的薄膜产品基片材料选用99.6%Al2O3,相比较其它材料,它的损耗较低,弯曲强度特好,热导率较好,特别是工艺的进步,厚度0.254mm/0.127mm的基片质量稳定,所以大量采用,加之稳定的共晶工艺,可以与氧化铍(BeO)材料的优良散热性媲美。

氮化铝(AlN):散热性较好,但高频损耗大。

氧化铍(BeO):散热性极好,损耗较小;因其环保问题,逐渐被淘汰,

石英(SiO2):损耗极小,散热性差,在毫米波段至太赫兹有应用。

3.2 基片表面粗糙度

基片表面粗糙度通常为0.05~0.1μm;较好的解决了损耗和金属与基板材料结合性问题。

3.3 电阻

采用TaN,50Ω/方电阻。

TaN电阻值理论可取10~200Ω/方,但其工艺稳定区域为10~100Ω/方;为了标化和成本一般取50Ω/方。

NiCr电阻也是可用做电阻薄膜的材料之一,阻值可取40~400Ω/方,但其稳定性较TaN差,我们不采用。

3.4 最小电阻尺寸:50μm

20μm也可以制做,但会造成电阻精度较低,所以一般设计电路时尽量避免。

3.5 电路焊盘

金线焊接通常有两种方式:楔形焊接(wedge bonding)和球形焊接(ball bonding),给予金线焊接的可靠性,根据不同工艺焊盘的最小尺寸如下表。

| WIRE SIZE(MILS) | TYPE | PAD SIZE(TIMES) |

| 0.7 | Wedge(楔形) | 1.5 |

| 1 | Wedge(楔形) | 2.25 |

| 0.7 | Ball(球形) | 2 |

| 1 | Ball(球形) | 3 |

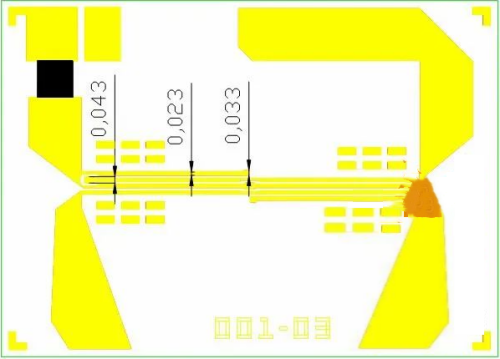

但对于结构需要导线较窄,同时需要金线焊接,例如耦合器,焊盘结构处理见下图:

3.6 石英基材的薄膜电路。

以石英为基材的薄膜电路可以应用到太赫兹,电路厚度最小可以到0.03mm,最常用厚度尺寸:0.05mm;0.076mm;0.127mm;0.254mm;其电路图形精度同通用电路,外形公差可以精确到0.015mm;本材料的使用需关注热变匹配问题。

3.7 电路的接地

电路的接地有两种方式:电路通孔金属化接地和金带焊接(welding)接地。

通孔金属化接地:主要针对结构空间小同时大电流情况下采用此方案,因其电路制造周期和成本问题,较少采用此方法。

金带焊接(AU Ribbon Welding)接地:

方法一因组装简便可靠,最为常用。方法二组装繁琐,仅在结构受限情况下采用。

4 薄膜电路工艺规范

1.0 目的

1.1本文件定义了薄膜电路的设计准则并适用于华诚制造的所有薄膜电路。

1.2本文件有三部分:

1. 基本设计原则。

2. 光刻板的设计要求。

3. 电阻设计原则。

2.0 基本设计原则

2.1 基板材料、厚度必须确定。

2.2 基板表面金属必须定义,包括基板两面的金属类型、厚度和公差。我们通常基板正面Au的

厚度为 3.4~4.0µm (135~160 microinches);我们通常基板背面Au的厚度为大于1µm (40microinches)。

2.3 我们的标准工艺要求电路外形必需为正方形或长方形。

2.4 所有电路的特征形状需由直线、圆弧、或它们的组合构成;不规则曲线不允许。

2.5刻蚀法:最小导线的线宽为10µm (约0.0004"),此适用于Au的厚度≤4µm (约160 microinches)。电镀法:最小导线的线宽为20µm (约0.0004"),此适用于Au的厚度≤4µm (约160 microinches) .

2.6 刻蚀法:导线的间隙最小为20µm (约0.0008"), 此适用于Au的厚度≤4µm (约160 microinches); 15µm (约0.0006”) 的间隙也可达到。电镀法:导线的间隙最小可做到10µm (约0.0004"),此适用于Au的厚度≤4µm (约160 microinches)。

2.7关键部位尺寸公差为 ±2.5µm (±0.0001"),此适用于Au的厚度≤4µm (约160 microinches);非关键部位尺寸公差为±7.6µm (±0.0003")。

2.8 Au的厚度标准公差为±20%。

2.9 电阻的长度、宽度最小值为50.8µm (0.002")。

2.10 TaN电阻有稳定的薄膜电阻值为50 ohms/square;如果需要,其它阻值可定制。电阻的标准公差为±10%。

2.11 含有薄膜电阻的电路必需设计一个独立的50 ohms 测试电阻,这对于无测试电阻的电路设计是尤为重要。

2.12 导线和电阻距电路边沿最小距离为50µm (约0.002")。(见图1)

2.13 所有电路在导线层应有识别标示。(见图1)

2.14 切割标记位于导线层,推荐标记尺寸为0.1mmx0.5mm (0.004”x0.02”)十字架(见图2)所示。

2.15 标准的最终电路尺寸公差为±50µm (0.002")。

3.5 电路排布图

3.5.1 光刻板的排列布置依据电路的尺寸和定制数量,排列布置确定基片尺寸、利用率及最后电路的造价。如果用户自己排列布置光刻板,请联系我们以确定最佳方式。标准的排列尺寸是2.0″×2.0″(50.8 mm×50.8mm),2.25″×2.25″(57.2 mm×57.2 mm)和 3.0″×3.0″(76.2 mm×76.2mm)。

3.6 基片材料

下面是材料系列

| Alumina (Al203)Asfired surface finish | Alumina (Al203)Polished surface finish | |

| 共烧氧化铝(Al2O3) | 抛光氧化铝(Al2O3) | |

| 材料厚度 | 0.005" | 0.005" |

| 0.010" | 0.010" | |

| 0.015" | 0.015" | |

| 0.020" | 0.020" | |

| 0.025" | 0.025" |

其它材料也可以供应,包括氧化铍(BeO)、氮化铝(AlN)、石英。

4.0 电阻设计准测

4.1 电阻的阻值由电阻的长度对宽度比例来决定,并用多少“squares” 来表示。

4.2 计算电阻阻值的方程式:

R = s(L/W)

R=电阻值(单位:ohms)

s=薄膜电阻值(单位:ohms/square)

L=电阻的长度尺寸

W=电阻的宽度尺寸

4.3 电阻的长度永远是指平行于电流方向的电阻尺寸。

4.4 电阻在角部(例如:L形或折弯形)的正方形,取薄膜电阻值的二分之一(见图5)。

4.5 电阻的类型

4.5.1 矩形形状:最常用类型电阻(见图6)。

4.5.2 L形或折弯形状:电阻在角部(例如:L形或折弯形)的正方形,取薄膜电阻值的二分之一。(见图7)

4.5.3 蛇弯形状:该形状通常用于大阻值的电阻,角部的数量使电阻值计算变得复杂,电阻在角部(例 如:L形或折弯形)的正方形,取薄膜电阻值的二分之一。(见图8)

5 薄膜电路制造标准MIL-STD-883(美国军用标准微电子器件试验方法和程序)规范

6 薄膜电阻额定功率计算

6.1 简单计算电阻额定功率

以下计算是基于99.6%AL2O3基片焊接于载体为0.635mm的科瓦合金。

a)以50欧姆/方为例:额定电流和电阻的宽度成正比例,通常计算按每1微米电阻宽度,额定电流为0.5~0.8毫安。

b)AU导线:额定电流和截面积成正比,一平方微米的额定电流为6~8毫安

6.2 精确计算电阻额定功率

电阻额定功率计算是基于热分析基础,TaN电阻本身的高温性能很好,即使在400℃,其物理性能也稳定,所以热分析主要为高温对系统参数的影响。

热分析时主要影响参数:

功率密度(W/CM2):功率密度是一个重要参数。

电阻尺寸:小尺寸的电阻,可以承受更大的功率密度,例如127微米的独立方阻可以承受的功率密度2300W/CM2。

电路基板:基板的厚度,在大功率情况下对于热传导影响巨大。

载体材料:不同的载体材料,会影响电阻的热传导,如:钨铜合金明显优于科瓦合金。

下图为电阻的热分析数据:

测试状态:0.381MM的99.6%AL2O3基片,电阻功率密度310W/CM2,工作环境温度85℃;载体为0.635mm的科瓦合金和钨铜合金。

三 微组装工艺技术

微波行业的微组装工艺是基于微波产品小型化过程中,产品组装特点而形成的一套工艺技术规范,相比较传统电装工艺,无论从环境、设备、辅助材料、工艺方法、人员要求培训等方面完全不同,该工艺技术在90年代已在国外成熟运用,国内在最近十年已开始运用薄膜电路和LTCC电路制造,目前已有工业化生产的专业企业;盒体、载板及涂敷技术与原有军品的盒体及涂敷技术雷同;对于微波产品制造商而言,建立自己的微组装工艺体系最为关键,微组装技术以工艺过程划分,主要有如下:

a)清洗

清洗是微组装过程中关系到产品可靠性的重要环节,原传统电装采用的化学和超声波清洗不能满足要求,通常采用合理的化学和等离子清洗,等离子清洗时介质气体的选择使用比较关键。

b)器件固定

以采用共晶焊接为主,焊料选择必须考虑到能满足整体工艺组装要求,要考虑器件散热、金属系的匹配、浸润性、合理的焊接温度匹配,焊料用量的控制和浸润无空气穴需加控制;导电胶粘接也是方法之一,接地电阻和可靠凝固需关注。

c)互连

常用互连方法是金线、金带焊接(wire bonging、Ribbon welding);金线互连分为球型焊接和楔型焊接(ball bonding、wedge bonding),焊接过程中建立其一致性的规范由为重要。

d)监控

显微镜目测器件及互连可靠性、金线拉力测试、器件固定后的剪切力测试。

e)封焊

是基于上述工艺稳定可靠后,对于可靠性要求极高的产品,采用的一种工艺技术,常用的有平行缝焊和激光焊接技术。

f)检漏

基于密封的结果监测,与原密封监测的设备和过程相同。

关注微博

关注微博 关注微信

关注微信 关注公众号

关注公众号 关注抖音号

关注抖音号