天华中威科技微波小课堂_一种基于ATE的SerDes物理层测试方法

天华中威科技微波小课堂:一种基于ATE的SerDes物理层测试方法

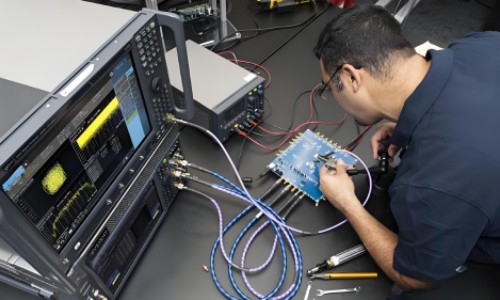

串行传输技术特别是串行解串器 (SerDes) 能提供比并行传输技术更高的带宽,被广泛应用于嵌入式高速传输领域。SerDes 物理层的测试需要设备的带宽大于信号速率,测试指标高且测试端口接入会对信号产生影响。大多数厂商采用仪器仪表与评估板来评估待测器件 (DUT) 的方式效率低下,只适用于产品评估阶段。基于自动测试设备 (ATE) 与可测性设计 (DFT) 相结合的方式,采用高速串行接口源同步测试技术、测试通路校准与补偿等技术,对 SerDes 产品的功能、发送和接收端参数进行全面的测试,实现高速接口的快速准确测试,并可适用于其他同类 SerDes 芯片测试。

1 引言

随着大数据时代的来临,数据传输对总线带宽提出了更高的要求。串行传输技术特别是串行解串器(SerDes)能提供比并行传输技术更高的带宽,所需芯片引脚数目较少而且支持通信、网络、数据存储、传输、超高速等多种主流的标准,现已广泛用于嵌入式高速传输领域。国内外高性能的 CPU、DSP、FPGA 等产品都内嵌了高速串行接口。高速串口技术的发展方向仍是提升单通道速度和多通道并行使用相结合。整体结果是提供不断改进升级的数据总带宽。

由于 SerDes 测试所需测试设备的带宽要大于信号速率,测试指标高且测试端口接入会对信号产生影响,因而对 SerDes 的物理层测试提出了较高的要求。

芯片设计商通常的方式是采用仪器仪表与评估板的方式对被测器件(DUT)进行评估。这个需要使用多套环境进行测试,其中包括波形发生器、示波器、误码率分析仪等,该方式测试结果准确但效率低下,只适用于产品评估阶段。另外还有采用 FPGA 的方式,该方法可以覆盖不同层的测试还可以使用用户的协议来保证安全性等,这也使得该方法的通用性相对差一些,需要针对一个产品做一个环境。为了解决测试效率和高指标问题,还可以采用 ATE 与测试仪表组件的方式进行,测试效率虽然没有 ATE 高但是相对于评估板的方式较容易接收。

本文通过使用 ATE 与产品的可测性设计相结合,对 SerDes 产品进行全面的功能、接收端参数、发送端参数的测试,测试快速准确,达到了很好的效果。与其他方法相比,该方法效率高,可以达到较高的指标,成本较受控。

2 SerDes 电路结构及其测试内容

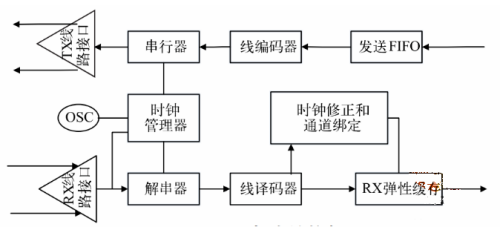

典型的 SerDes 电路结构如图 1 所示。一个最典型的 SerDes 电路发送端的内部结构至少应包括串行化电路、编码电路,通常在编码电路之前还有一级Scramble 编码电路以减小信号的高频谐波分量及信号失真;接收端应至少包括解串电路、解码电路、CDR时钟数据恢复电路等。其他可能包括的功能模块有:

循环冗余检测(CRC)码生成器、CRC 检测器、多种编码和解码(4b/5b、8b/10b、64b/66b)、可调的扰码器、各种对齐和菊花链选项、可配置的时钟前端和后端以及不同等级的自环。

图 1 SerDes 电路结构框图

2.1 功能测试

SerDes 电路的功能测试采用 ATE 与内部可测性设计相结合的方式。SerDes 中通常有测试电路,其中伪随机二进制序列产生与检测器用于产生 PRBS 码和对数据的检测。

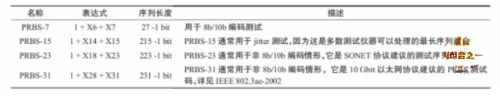

PRBS 伪随机序列通常被用于高速接口的信号完整性测试中。这些序列看起来是随机的,但事实上具有特定的属性,可以用来测量链路的质量。在 SerDes中收发器的数据发生模块可以产生多种工业标准的伪随机序列,如表 1 所示。同时为了实现 SerDes 电路的自检,全双工的 SerDes 通常有环回测试路径,包括近端 PCS 环回、近端 PMA 环回、远端 PMA 环回、远端PCS 环回。同时在 ATE 端可进行外环回测试。

表 1 伪随机序列组合

2.2 性能测试

根据应用领域的不同,JEDEC、IEEE、ITU-T 和OIF 等多个标准中对 SerDes 的物理层接口和抖动等的特性进行了规定。例如 JESD204B 标准第 4 章中对接收端和发送端电气特性做了明确的规定。

SerDes 的电气特性参数分发送端和接收端。发送端的参数主要包括预加重和去加重输出幅度、预加重和去加重输出峰峰值、共模电平、输出抖动幅度等。接收端的参数主要包括共模与差模电压、上升下降时间、输入抖动容限、本地时钟抖动容限等。

3 测试难点

3.1 源同步技术

高速数字接口不断增加的数据传输速率使得数据同步成为各项功能项、交直流参数等测试的关键前提。这个问题主要是由于时钟抖动造成数据无法采样带来的。本文通过一系列电平和时序调整确认同步点位置、最终找到最佳采样点的方式以解决此问题。

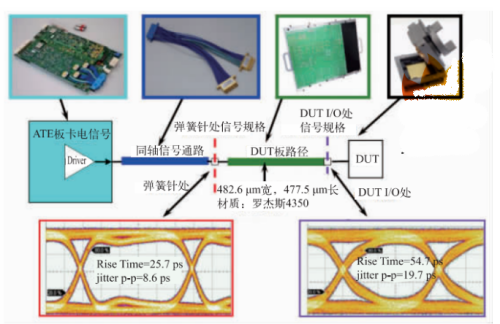

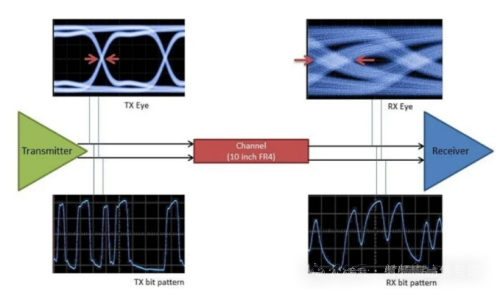

3.2 测试通路校准与补偿

高速信号的测试必须保持通路上的信号质量,图2 是信号在整个通路的衰减过程。需要在硬件设计中特别考虑信号完整性问题,PCB 绘制中除做到一组等长外,有多路信号进行测试时需要进行多路等长,确保TDR 之后各路信号同步。在幅度上对于前期硬件设计不合理的需要同步幅度补偿来确保芯片评价的正确性。

图 2 测试通路上信号衰减过程

4 测试实现

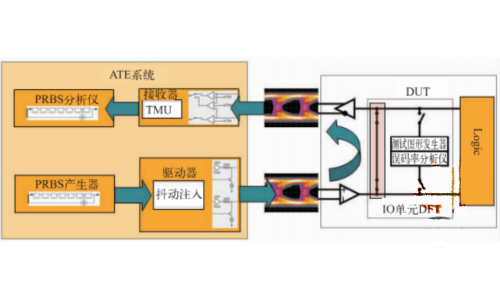

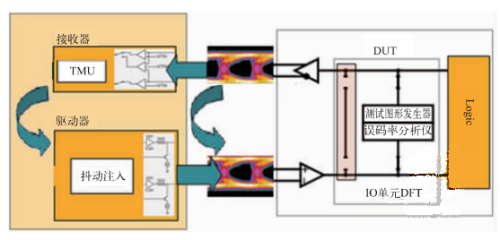

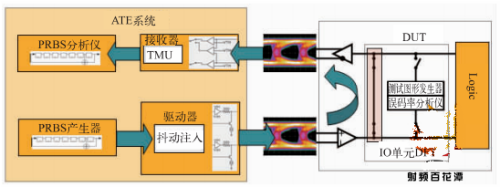

本项目选用 93K 作为实现平台。整个产品测试实现的环路如图 3、4 所示。

图 3 环回测试路径

图 4 参数测试路径

4.1 自环测试

自环测试可以大大降低对测试设备的通道和速度要求,对不支持自环测试的源同步总线,可通过外围电路为高速总线建立自环回路来支持自环测试。该方法的缺点是无法对性能和参数进行测试。

4.2 数据采集和解码分析实现

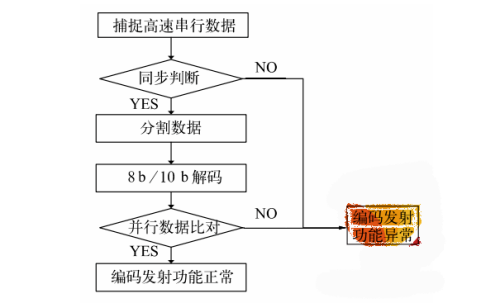

使用高速模块向 RX 端发 PRBS 码后,经过芯片后在 TX 端用高速模块将串行数据全部采集下来后,通过软件方法对数据进行遍历,寻找同步关键字,在此基础上对数据进行分割,最后用查表方式对串行数据进行解码,再在此基础上将解码数据和发出数据进行对比,判断发送功能是否正确。具体流程如图 5 所示。

图 5 高速 SerDes 电路功能测试流程

4.3 高速串行数据编解码算法实现

高速串行数据编解码算法主要是 8b/10b 编解码算法的实现,难点是权重的计算。具体的算法是在发送的码中增加固定码的同步信号,将采集进来的信号和固定码的编码值进行比对查找,找到采集数据码流的字节分割点对数据进行 10 位一组的分割,然后将分割好的数据变成高 4 位和低 6 位,然后利用编码表进行反向查表,即可得到原始发送数据的数据值。

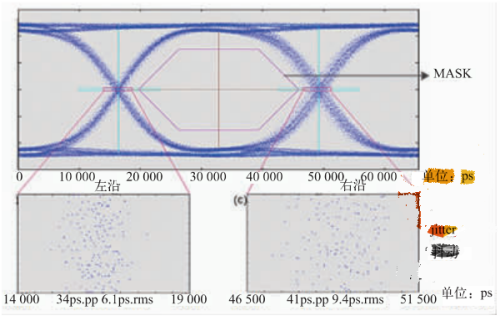

4.4 高速输出端口交直流参数测试实现

利用 ATE 对端口数据进行数字采样,经过对数据采样点进行处理,重新建立眼图;进行数据直方图分析,寻找高和低电压检测眼图的边缘,用离散傅里叶变换对眼图进行处理,建立眼图 mask,便可从眼图边缘数据分布计算出数据抖动。眼图 mask 的建立基本解决交流参数的测试。眼交汇处可计算出信号的抖动情况。图 6 是左边沿和右边沿整体与放大的波形。

图 6 ATE 测试眼图

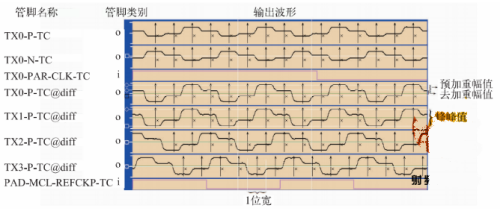

有的 SerDes 还具有预加重和去加重功能,可通过内部设置使芯片处于该工作模式下,在输出端测试预加重和去加重输出幅度等,如图 7 所示。图中所示可非常清晰地查看到第一和第二电压幅度。

图 7 预加重和去加重输出波形

4.5 高速输入端口交直流参数测试实现

高速输入端口的测试需要对高速串行信号加入一定的扰动。需要抖动的幅度和频率可控,模拟环境中的时钟抖动。将此信号送入待测器件的高速输入端,调节抖动的幅度来测试解码模块的输入容忍度。

5 结论

由测试结果可得出该方法可以比较直观地查看测试图形与结果,同时测试结果可一键输出,数据也可按统一格式输出,便于快速地对 SerDes 接口进行测试与分析。同时该方法还有很好的通用性,可用于其他同类 SerDes 芯片的测试,包括专用电路与内嵌 IP等。该方法目前已实现 10.125 Gbit/s 的测试,最高可实现 16 Gbit/s 的测试。

作者:张凯虹,季伟伟,朱 江

来源:电子与封装

关注微博

关注微博 关注微信

关注微信 关注公众号

关注公众号 关注抖音号

关注抖音号