[设计研发]基于AD9154的八通道信号产生器设计

[设计研发]基于AD9154的八通道信号产生器设计

JESD204B 是一种高速串行总线协议,主要应用于转换器与 FPGA 的数据传输接口,和并行数据总线相比有着明显的优势。AD9154 是一款具有 JESD204B 接口的四通道模数转换器(DAC)。现场可编程门阵列(FPGA)可产生数字波形信号,其高速串行收发器接口可通过 JESD204B 总线协议将波形数据发送给 AD9154 芯片产生模拟信号。使用 2 片 AD9154 与 1 片 FPGA 为核心器件,完成硬件电路和软件程序设计,最后测试了产生信号的技术指标。

随着转换器分辨率和速度的提高,对更高效率接口的需求也随之增长。JESD204 不但带来了高效率,并提供了CMOS 和 LVDS 不能满足的速度、大小和价格等优势。由于其管脚较少,可以降低封装大小,使电路板布线更加简便,还能降低整体成本。由于其标准的扩展性,能适应未来设计的需要。自 2006 年发布以来,JESD204 已推出了两个版本,现行的是 B 版本,即 JESD204B。随着该标准被转换器供应商和FPGA 制造商等用户采用,变得更加精确,也增添了更多的功能,提高了效率和操作的简便性。此标准适用于 ADC 和 DAC,也可以用作 FPGA 的通用接口。

1 JESD204B 协议

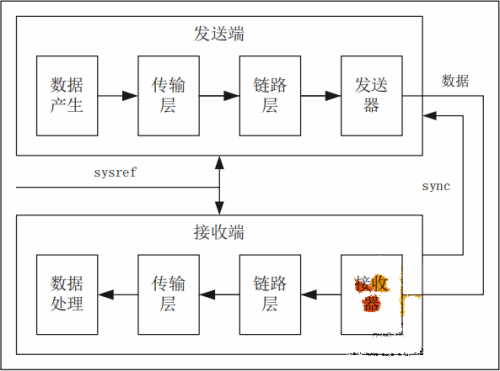

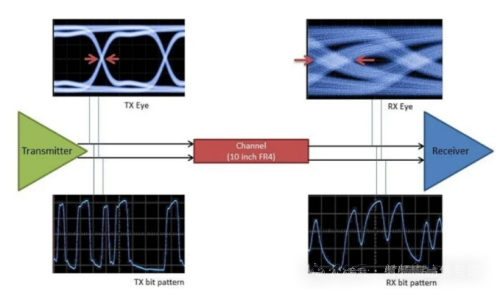

JESD204B 接口包括发送接口和接收接口,其结构分为物理层、数据链路层、传输层和应用层,接收接口在功能上可以视为发送接口的逆过程。其结构框图如图 1 所示。物理层实现高速串行信号的发送和接收,完成数据串并、并串转换以及编解码处理。接口采用电流模式逻辑(CML)驱动器和接收器的差分对组成,传输速率为 312.5Mbps~12.5Gbps。数据链路层实现 8B/10B 编解码、确定发送 / 接收规则、码组同步、字符替换、SYNC 信号对齐、初始化帧同步、帧队列检测和校准等功能。对于发送部分,传输层实现将采样数据组成帧,把帧传输给链路层 ;对于接收部分,传输层实现获取解码后的帧,将帧中的信息解码为采样数据进行处理。

图 1 JESD204B 收发结构图

JESD204B 通过三个阶段来建立同步链路 :代码组同步(CGS)、初始通道同步(ILAS)和数据传输阶段 。链路需要共享参考时钟、数据通道、同步信号。JESD204B 协议定义了Subclass0、Subclass1、Subclass2 三类子集设备,本文用到的是目前使用最广泛的 Subclass1。其 Subclass1 需要sync 和 sysref 两个同步信号。建立连接的过程为 :CGS 阶段,接收端将 sync 信号拉低,发出同步请求 ;发送端发出 /K28.5/ 符号 ;接收端接收到至少 4 个无错误的连续 /K28.5/符号时,将 sync 信号拉高,同步成功。ILAS 阶段,发送端发送 4 个多帧,帧信息包括控制字符信息和配置参数信息。数据传输阶段,将组成帧的数据给接收设备。

2 硬件设计

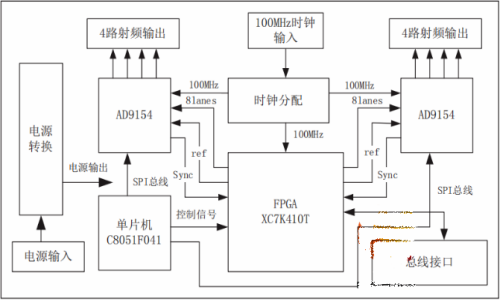

八通道信号产生器由 FPGA、单片机、DA、时钟分配电路、电源等组成。结构框图如图 2 所示。

图 2 八通道信号产生器结构框图

FPGA 是产生信号的核心器件,选用 Xilinx 公司 V7 系列的 XC7K410T。此系列 FPGA 具有丰富的 RAM 及 DSP 资源、高速 I/O 接口以及支持 JESD204B 的 GTX 资源,可满足高采样率波形数据计算及 JESD204B 协议传输需求。FPGA 通过自定义总线接收指令,控制载波、基带、调制和输出等模块协同工作,产生相应的数字波形数据,经 JESD204B FPGA 核将数据按照协议打包发送给数模转换器 (DAC),DAC 将数据解包后转变为模拟信号输出。单片机通过 SPI 总线完成对 AD9154的寄存器读写并产生对 FPGA 的控制信号。时钟模块可对内外 100MHz 时钟进行选择,并将时钟进行分路分别供给 FPGA和 AD9154,用于电路板的正常工作。AD9154 是 ADI 公司于 2015 年推出的一款四通道、1GS/s、16 位数模转换器(DAC), 其片内集成 PLL(锁相环)和八通道 JESD204B 接口,在100~300MHz 频段内具有优异的动态范围性能。

3 软件设计

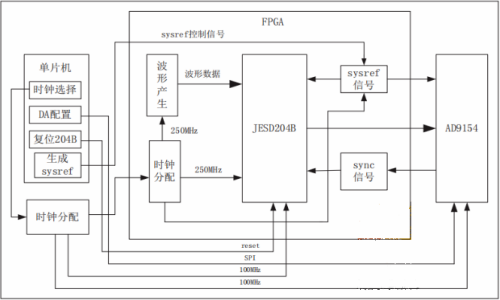

八通道信号产生器的软件包括FPGA 软件和单片机软件。其中,单片机完成时钟选择、DAC 寄存器配置、对 JESD204B 核的复位、和生成同步参考信号的功能 ;FPGA 完成时钟分配、波形产生、JESD204B 核的应用和同步信号的处理等功能。软件设计框图如图 3 所示。

图 3 软件设计框图

3.1 参数配置

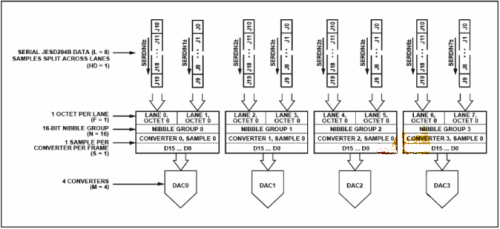

八通道信号产生器设计工作模式为DAC 采样率 1Gsps,四通道输出、每路 LANE数据传输速率为 10Gsps,根据以上条件,JESD204B 的关键配置参数为 :

使用的 lanes 数量(L)=8 ;

决定采样信息是否包含在一条 lane 中(HD)=1 ;

每 条 lane 在 一 个 帧 周 期 中 octets(8bits)的数量(F)=1 ;

转换器分辨率(N)=16 ;

每个帧周期中每个转换器采样数据数量(S)=1 ;

转换器件数量(M)=4。

根据以上参数配置,DAC 的数据传输如图 4 所示。

图 4 DAC 数据传输框图

3.2 单片机程序设计

单片机完成时钟选择、DAC 寄存器配置、对 JESD204B 核的复位、和生成同步参考信号的功能。单片机程序的核心为 DAC 寄存器的配置,其实现对 DA工作模式、工作时钟、JESD204B 物理层、数据链路层、传输层等的配置。对 FPGA 的 JESD204B 核的复位后,发送和接收端的JESD204B 已经准备好了,这时候发送 sysref 信号完成 FPGA与 DAC 的时钟同步,可以进行数据链路的同步了。按照第 1 章所述的链路同步过程同步完成后,读取相应的寄存器可以得知 DAC 的工作状态,若状态正常,DAC 和 FPGA 建立连接成功且工作完成 ;若不正常,进行重同步。

3.3 FPGA 程序设计

FPGA 完成时钟分配、波形产生、JESD204B 核的应用和同步信号处理等功能。

FPGA 程序设计首先完成对 JESD204B 核的配置和生成,按照设计的工作模式和参数配置核并产生核文件 ;JESD204B核完成对发送接口物理层、数据链路层、传输层等的配置,对外接口主要包括时钟、高速数据、同步、并行数据、AXI 控制总线接口等。其中,时钟为 JESD204B 的 250MHz 工作时钟 ;高速数据接口为与 DAC 传输数据的 8 对 GTX,工作速率为 10Gsps ;同步接口包括接收 sync 同步信号和 sysref 信号。时钟分配模块实现用 100MHz 的时钟产生设计需要的时钟,包括主工作时钟 250MHz,控制接口时钟 20MHz。波形产生模块实现产生发送给 DAC 的波形数据,因 DAC 的采样率为 1Gsps,FPGA 产生波形的速率为 250MHz,故采用用资源换速度的策略,即在一个 250MHz 时钟周期内,FPGA 并行产生 4 个波形采样点的幅度数据,用 DDS 技术产生正交载波。利用正 / 余弦波形的对称性,使用一个双口 ROM 存储 1/4 个周期的波形,即可通过查表控制来产生完整周期。同步信号处理实现将单片机输入的同步控制信号转变为与主时钟同源的信号,用于同步 DAC 和 FPGA 的时钟。

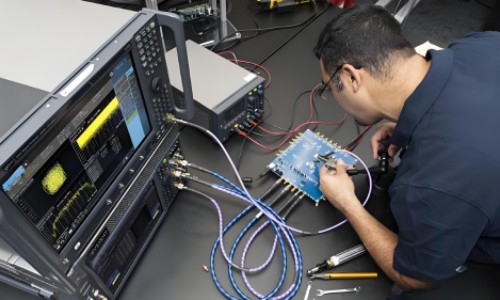

4 测试结果

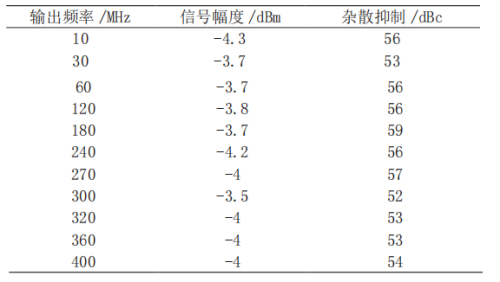

八通道信号产生器按照图 2 所示的硬件结构进行了设计制造,按照图 3 所示软件结构进行了单片机和 FPGA 程序设计,对输出信号进行了测试。使用 Agilent 的信号分析仪N9020A 对输出信号进行频谱测量。针对单音信号,部分频点的信号幅度及杂散抑制值如表 1 所示。测试结果表明,输出信号能够达到 400MHz 带宽,带内杂散抑制在 50dBc 以上,幅度一致性在 1dB 以内,达到工程应用要求。

表 1 八通道信号产生器测试结果

5 结束语

本文设计的八通道信号产生器,结合大容量 FPGA 与JESD204B 接口的 DAC,只用一块板卡就可以产生八通道400MHz 带宽的任意波形信号。对硬件板卡和程序软件都进行了精心设计。经实际测试和工程应用,达到了设计要求。八通道信号产生器具有设备简单、幅度一致性好、波形配置灵活等优点,利于降低设备复杂度、控制成本,可广泛应用于宽带通信对抗、复杂电磁环境背景信号产生等领域。

作者 :冯鹤 来源:设计研发

关注微博

关注微博 关注微信

关注微信 关注公众号

关注公众号 关注抖音号

关注抖音号