[行业动态]2nm为什么这么贵,贵在哪里?

近日,日本Rapidus首席执行官 Atsuyoshi Koike 在接受《日经新闻》采访的时候表示,与目前其他日本公司生产的标准芯片相比,2nm芯片的成本将增加十倍。Rapidus是日本政府支持的半导体财团,其成立目的是超越世界领先的芯片制造商。他们认为,其2nm芯片对日本至关重要,因为其中一些芯片将用于对国家安全至关重要的高性能计算应用,而其他芯片也能用于自动驾驶汽车和机器人等创新民用应用。

“2nm芯片将比当今先进节点制造的芯片贵得多,与当今日本制造的‘主流’芯片(45nm)相比,价格上涨十倍,这是一个巨大的飞跃。”Atsuyoshi Koike说。不过,即使如此贵,Atsuyoshi Koike预计,在他们于2027年开始量产2nm之后,也有公司愿意为此买单。

芯片的成本构成

众所周知,随着SoC变得越来越复杂,围绕它们的经济因素也变得越来越复杂。其中包括要集成的功能和IP、上市速度、功率和性能规格、金属层数、存储器的配置方式和使用的存储器数量以及目标市场等所有内容。其中每一个都有一个价格,并且它们加起来可以是一个非常大的数字。

Synopsys也在一篇博客文章中表示,每个芯片设计项目都是独一无二的,但有五个基本因素会影响总体成本:

第一是内容库(Content Libraries);据介绍,所谓内容库由芯片设计项目中使用的第三方IP组成,包括常用功能、输入和输出(I/O)电路以及片上存储器。内容库许可费各不相同,但可能高达数千万美元。此外,公司还必须支付每个芯片的使用费,这应该计入项目预算。

第二是EDA工具;EDA工具可用于虚拟布局电路、模拟操作和验证性能。EDA软件有多种形式,包括本地、云托管和软件即服务(SaaS)。定价可以基于许可、基于使用或两者的组合。此外,EDA工具还需要强大的计算机和大量存储容量,这意味着需要投资本地或云基础设施。

第三是制造芯片的代工厂按硅片收费;芯片越小,组织在每个晶圆上可以获得的芯片就越多。然而,随着芯片尺寸变小,其他设计成本(例如研发成本)也会变得更高。控制芯片设计成本意味着在高效晶圆使用和现实研发之间找到平衡。

第四是时间;产品进入市场的速度越快,项目的整体投资回报率就越高。除了设计芯片所花费的时间之外,公司还必须考虑流片和代工生产之间的滞后时间。每个设计都存在缺陷,在生产开始之前,设计师和晶圆厂必须解决这些缺陷。

最后,生产前的最后一步包括预测新芯片的需求并向代工厂承诺订单。这是一项复杂且高风险的操作。如果您订购的芯片太少,您将出现供应短缺并可能会损失销售;如果您订购太多,您可能会在未使用的库存上浪费数千甚至数百万美元。

此外,工艺的良率,芯片设计的质量和封测,也都是芯片的成本构成,由此可见,计算芯片的成本,并不是一件简单的事情。

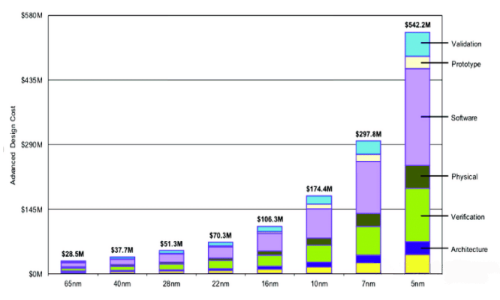

相关资料显示,在主流节点(40纳米到65纳米)上,如果从头开始,新芯片的价格大约为4000万美元到5000万美元之间。但这些节点的良率很高,而且软件开发成本也较低,且这些芯片在功能上并不处于领先地位,那就意味着往更先进的工艺前进,成本会继续飙升。这从IBS提供的数据可以看到。如图所示,进入到5nm时代,芯片的设计成本可以飙升到5.4亿美元,在工艺继续往后走,成本的继续升高是可以预期的。

不同工艺节点下的芯片设计成本

2nm,贵在哪里?

要讨论2nm贵在哪里,如上所述,这同时是一个复杂的问题。

不过,据笔者从相关供应链了解到。进入了这些先进工艺,无论是IP,还是EDA工具,其成本的提高都是能够理解的。而进入到这些先进芯片,因为一次性流片成本较高,这就使得相关验证成本水涨船高,这从IBS提供的上图可以看到,进入到2nm芯片时代,设计的成本是可以预期的。

值得一提的是,伴随着这些先进工艺而生的是先进制造和封装工艺,这带来的成本也是不容忽视的。

以制造端为例,根据IBS对晶圆厂的先进工艺投资测算,如果要建设一个3nm工艺,月产4万片的晶圆生产线,成本约为150亿到200亿美元。据台湾联合报之前报道,台积电将斥资1万亿新台币(约合339亿美元)在台湾台中市建造一座晶圆厂,生产2纳米芯片。Rapidu首席执行官Atsuyoshi Koike此前在接受采访时曾表示,公司需要投入2万亿日元用于研发才能开始试生产2nm,然后需要投资3万亿日元才能开始量产2nm芯片。

其中,EUV光刻机和相应配套材料的成本增加,必然会是一个重要影响因素。

从DUV往EUV光刻机推进的时候,作为芯片制造的主要成本之一的环节光刻成本有了新的提升。但在即将进入的high na euv光刻制造时代,单台光刻机的制造成本将会从1亿多直接飙升到三亿多。虽然芯片在制造中使用的EUV的层数不会太多,例如据相关报道,在3nm工艺的时候,会采用多大25层EUV光刻曝光工艺。由此可见,这在进入2nm时代,势必会带来成本的提升。

进入到EUV时代,还有一个辅料需求增加,且成本会飙升,那就是掩模组(mask set)。

按照Semianalysis的报道,在90nm至45nm的代工工艺节点上,掩模组的成本约为数十万美元。28纳米工艺的价格已超过100万美元。对于7nm,成本增加超过1000万美元,而现在,当我们跨越3nm障碍时,掩模组将开始进入4000万美元范围。

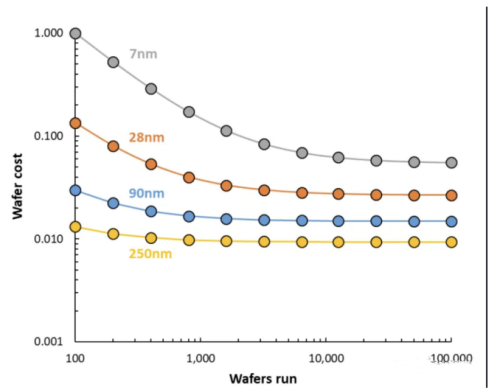

图片晶圆成本的变化

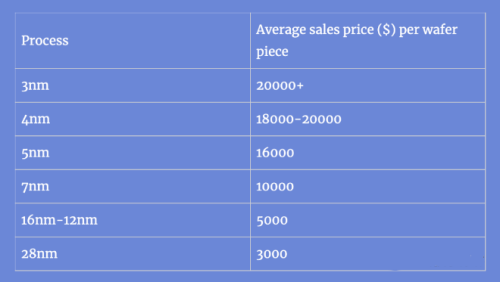

关于芯片制造成本的飙升,我们可以从台媒泄露的台积电在相关晶圆报价上略知一二。

据Digitimes报道,与N5(5纳米级)生产节点相比,台积电将把使用其领先的N3(3纳米级)工艺技术加工的晶圆的价格提高25%。换而言之,采用台积电领先的N3制造技术加工的一块晶圆将花费超过20,000美元 。作为对比,N5晶圆的成本约为16,000美元,如下图所示。

报道进一步指出,台积电将为其即将推出的2nm节点进一步提高芯片生产价格。新的晶圆价格预估表明,台积电将对2nm芯片每片晶圆收取25,000美元的费用。

谁在竞争2nm?

正因为2nm无论是芯片设计还是建造晶圆厂成本都是如此昂贵,所以可以预期的是,仅有少量的厂商能够跨入2nm这个阶段。在Fabless方面,我们认为英伟达、苹果、高通、MTK和博通等领先厂商会是首批使用2nm的客户。在晶圆制造方面,则和大家所了解的一样,除了台积电、三星和Intel以外,文章开头提到的日本Rapidus会是其中的一个玩家。

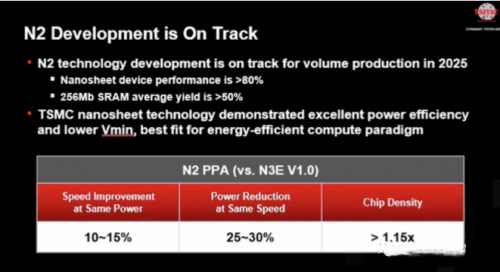

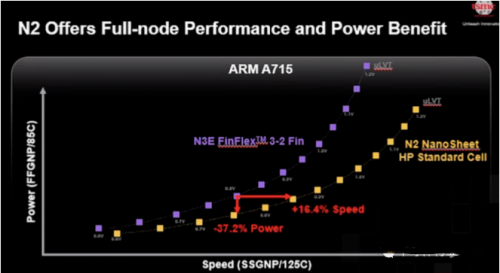

首先看台积电方面,他们在去年首先推出初始版本的2nm工艺是该代工厂第一个使用环栅(GAAFET)晶体管的节点,台积电将其称为Nanosheet晶体管。与当前FinFET晶体管相比,GAAFET的优势包括降低漏电流(因为栅极位于沟道的所有四个侧面),以及调整沟道宽度以获得更高性能或更低功耗的能力。

台积电去年推出这项技术时表示,在相同功耗和复杂度的情况下,可以将晶体管性能提升10%到15%,或者在相同时钟和晶体管数量的情况下,将功耗降低25%到30%。该公司还表示,N2将提供比N3E高15%以上的“混合”芯片密度,这比去年宣布的10%密度增加有所增加。

在今年的技术大会上,台积电表示,N2技术开发已步入正轨,该节点将于2025年进入大批量生产(可能是2025年很晚)。该公司还表示,在进入HVM两年前,其Nanosheet GAA晶体管性能已达到目标规格的80%以上,256Mb SRAM测试IC的平均良率超过50%。

台积电的N2系列将在2026年的某个时候升级,届时该公司计划推出其N2P制造技术。N2P将为N2的Nanosheet GAA晶体管添加背面电源轨技术。公司还在准备N2X——一个专为高性能计算(HPC)应用(例如需要更高电压和时钟的高端CPU)量身定制的制造工艺。

在三星方面,他们也表示,公司也将于将于2025年开始大规模生产用于移动应用的2nm芯片。三星还将在2026年提供用于高性能计算的2纳米芯片生产,并在2027年提供汽车芯片的工艺。

该公司表示,与去年推出的3nm工艺相比,其2nm工艺的性能和能效分别提高了12%和25%,是芯片制造商中率先做到这一点的。三星表示,其2nm工艺还提供比3nm工艺小5%的芯片。该公司还表示,将于2027年开始量产采用1.4纳米工艺的芯片。

来到Intel,他们在今年三月初的一场会议上透露,公司已经完成了其1.8纳米和2纳米制造工艺开发。该公司将于2024年开始在内部和第三方产品中使用1.8纳米和2纳米制造工艺。他们表示,Intel 18A每瓦性能提高10%。Intel 20A的每瓦性能提高了15%。

至于rapidus,他们则计划通过和IBM、IMEC等机构合作,以推进其2nm研发。

毫无疑问,在技术以外,这是一场当之无愧的金钱竞赛。

文章来源:光刻人的世界

关注微博

关注微博 关注微信

关注微信 关注公众号

关注公众号 关注抖音号

关注抖音号