[技术前沿]下一代光刻技术--高数值孔径EUV光刻

在过去的半个世纪中,我们开始将摩尔定律(即给定硅面积中的晶体管数量大约每两年翻一番,推动计算向前发展)视为刚刚发生的事情,就好像它是自然发生的一样。一个自然的、不可避免的过程,类似于进化或衰老。当然,现实却大不相同。跟上摩尔定律的步伐需要花费几乎难以想象的时间、精力和人类的聪明才智——跨越多个大陆的数千人以及地球上一些最复杂的机器的无尽土地。

也许这些机器中最重要的是执行是极紫外(EUV)光刻。EUV 光刻是数十年研发的产物,现已成为过去两代尖端芯片背后的驱动技术,在过去三年中用于每一款高端智能手机、平板电脑、笔记本电脑和服务器。然而摩尔定律必须继续前进,芯片制造商继续推进他们的路线图,这意味着他们需要进一步缩小设备的几何尺寸。

因此,在ASML,我(指代本文作者JAN VAN SCHOOT,下同)和我的同事正在开发下一代光刻技术。它被称为高数值孔径EUV光刻,涉及对系统内部光学器件的重大检修。高数值孔径EUV将于2025年投入商业使用,芯片制造商将依靠其能力在本十年末保持其承诺的进步。

光刻的3个因素

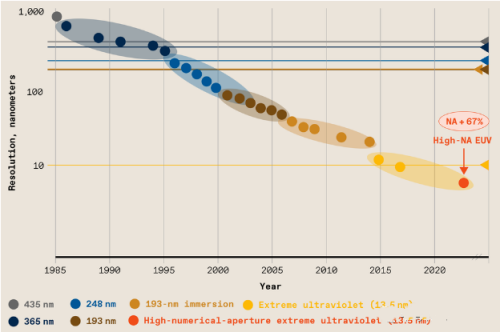

摩尔定律依赖于提高光刻分辨率,以便芯片制造商可以铺设越来越精细的电路。在过去35年里,工程师们通过综合研究以下三个因素,将分辨率降低了两个数量级:光的波长;k 1,封装过程相关因素的系数;数值孔径 (NA),衡量系统发光角度范围的指标。

临界尺寸(即使用某种光刻曝光工具可以打印的最小特征尺寸)与光的波长除以光学器件的数值孔径成正比。因此,您可以通过使用较短的光波长或较大的数值孔径或两者的组合来实现更小的临界尺寸。例如,通过改进制造过程控制,可以将k 1值推至尽可能接近其物理下限0.25。

一般来说,提高分辨率的最经济的方法是增加数值孔径并改进工具和工艺控制以实现更小的k 1。只有当芯片制造商没有办法进一步提高NA和k 1时,他们才会采取减小光源波长的方法。

然而,业界不得不多次改变波长。波长的历史进程从使用汞灯产生的365纳米,到20世纪90年代末通过氟化氪激光器产生的248纳米,然后在20世纪90年代初期,通过氟化氩激光器产生的193纳米。对于每一代波长,光刻系统的数值孔径都在逐渐增加,然后工业界才转向更短的波长。

例如,随着193 nm的使用即将结束,引入了一种增加NA的新方法:浸没式光刻。通过在透镜底部和晶圆之间放置水,NA可以从0.93显着增大到1.35。自2006年左右推出以来,193纳米浸没式光刻技术一直是尖端光刻技术的行业主力。

在过去四十年中,光刻技术的分辨率提高了约10,000 倍。这在一定程度上是由于使用了越来越小的光波长,但它也需要更大的数值孔径和改进的处理技术。

EUV的黎明

但随着打印小于30 nm的特征的需求增加,并且由于193nm 光刻的NA已达到极限,遵循摩尔定律变得越来越复杂。要创建小于30 nm的特征,需要使用多个图案来生产单层芯片特征(这在技术和经济上都是一项繁琐的技术),或者需要改变波长。我们花了20多年的时间和无与伦比的开发努力才将下一个新波长上线:13.5纳米EUV。

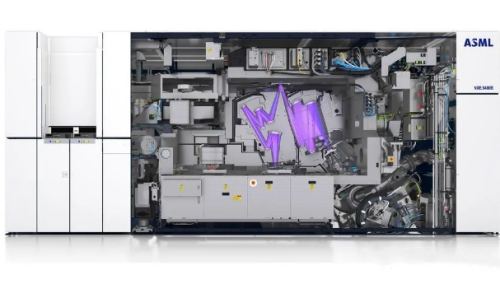

EUV需要一种全新的发光方式。这是一个非常复杂的过程,需要使用强大的zCO 2激光撞击飞行中的熔融锡滴,然后将锡蒸发成等离子体,发射出光子能量光谱。EUV光学器件从该光谱中获取所需的13.5 nm波长,并将其引导通过一系列镜子,然后从图案掩模反射,将该图案投影到晶圆上。所有这些都必须在超净真空中完成,因为13.5 nm 波长会被空气吸收。(在前几代光刻技术中,光线通过掩模将图案投射到晶圆上。但EUV很容易被吸收,因此掩模和其他光学器件必须是反射性的。)

在真空室中,EUV光 [紫色] 在从光掩模 [顶部中心] 反射之前经过多个镜子反射。从那里,光继续它的旅程,直到它被投射到带有光掩模图案的晶圆上[底部中心]。插图显示了当今数值孔径为0.33的商业系统。NA为0.55的未来系统中的光学器件将会有所不同。

从193纳米光转向EUV在一定程度上降低了临界尺寸。一种称为“制造设计”的过程,涉及设置电路块的设计规则以利用光刻的限制,在降低k 1方面发挥了很大作用 。现在是时候再次提高数值孔径了,从现在的0.33提高到0.55。

让高数值孔径EUV发挥作用

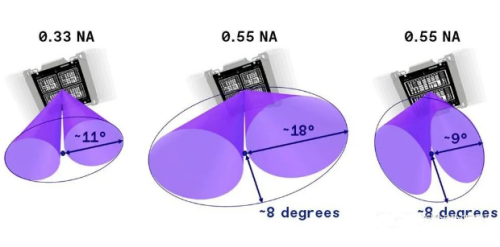

将NA从今天的0.33增加到目标值0.55不可避免地需要进行一系列其他调整。EUV光刻等投影系统在晶圆和掩模处都有NA。当您增加晶圆上的NA时,也会增加掩模上的NA。因此,在掩模处,入射和出射的光锥变得更大,并且必须彼此成一定角度以避免重叠。重叠的光锥会产生不对称的衍射图案,从而导致令人不快的成像效果。

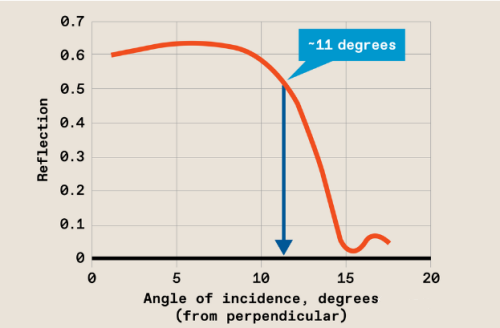

但这个角度是有限制的。由于EUV光刻所需的反射掩模实际上是由多层材料制成的,因此无法确保在特定反射角度以上获得适当的反射。EUV掩模的最大反射角为11度。还有其他挑战,但反射角度是最大的。

如果EUV光以太陡的角度照射光掩模,它将无法正确反射

当今EUV中掩模处的反射角已达到极限 [左] 增加EUV的数值孔径将导致反射角过宽 [中]。因此,高数值孔径EUV使用变形光学器件,该光学器件允许角度仅在一个方向上增加 [右]。以这种方式成像的场是一半大小,因此掩模上的图案必须在一个方向上扭曲,但这足以维持通过机器的吞吐量。

克服这一挑战的唯一方法是提高称为缩小的质量(The only way to overcome this challenge is to increase a quality called demagnification)。缩小就像它听起来的那样——从掩模上获取反射图案并将其缩小。为了补偿反射角问题,我和我的同事必须将缩小倍率加倍至 8 倍。因此,晶圆上掩模的成像部分将小得多。这种较小的像场意味着需要更长的时间才能产生完整的芯片图案。事实上,这一要求会将我们的高数值孔径扫描仪的吞吐量降低到每小时100个晶圆以下,这一生产率水平将使芯片制造变得不经济。

值得庆幸的是,我们发现只需要在一个方向上增加缩小倍数(demagnification),即发生最大反射角的方向。另一个方向的缩小率可以保持不变。这使得晶圆上的场尺寸可接受,约为当今EUV系统中使用的尺寸的一半,即26 x 16.5毫米,而不是26 x 33毫米。这种方向相关的或变形的缩小构成了我们高数值孔径系统的基础。光学器件制造商卡尔蔡司付出了巨大的努力来设计和制造符合我们新机器所需规格的变形镜头。

为了确保半尺寸场具有相同的生产率水平,我们必须重新开发系统的掩模版和晶圆台(分别固定掩模和晶圆的平台),并在扫描过程中使它们彼此同步移动。重新设计产生了纳米级精度的平台,加速度提高了四倍。

高数值孔径EUV将于2025年投产

第一个高数值孔径EUV系统ASML EXE:5000将安装在我们与比利时纳米电子研究机构Imec于2024年初联合开设的新实验室中。该实验室将允许客户、掩模制造商、光刻胶供应商和其他公司开发使高数值孔径EUV成为现实所需的基础设施。

我们必须使其成为现实,因为高数值孔径EUV是维持摩尔定律的关键组成部分。不过,达到0.55NA 并不是最后一步。从那时起,ASML、蔡司和整个半导体生态系统将以我们难以想象的方式进一步向更好、更快和创新的技术延伸。

关注微博

关注微博 关注微信

关注微信 关注公众号

关注公众号 关注抖音号

关注抖音号