天华中威科技微波小课堂_PCIe常见插槽速度对比

01 为什么要科普PCIe

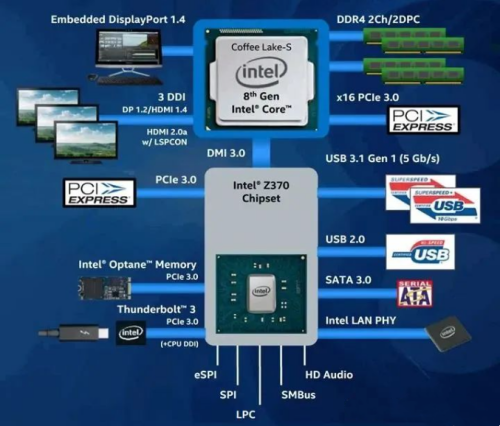

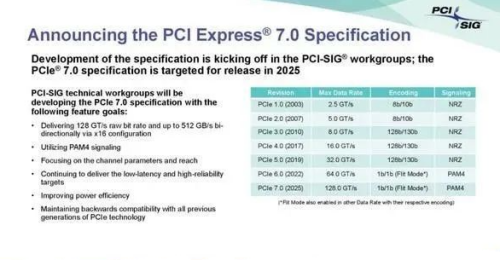

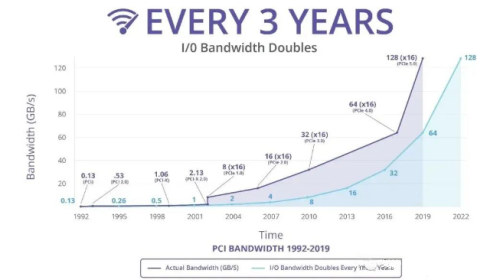

PCIe总线是服务器系统里最重要的总线,经过PCIe信号的互联,CPU得以与各种外设部件进行通信。如果我么比喻每个bit的数据是一辆小车,PCIe总线是车道,每条Lane是一条双向车道,PCIe版本规定了速度上限,由此就很好理解了,不考虑编码损耗的情况下,车道越多,允许的车速越快,通过的数据自然也就越多,PCIe 7.0 Base Specification目前刚刚发布Draft 0.3版本,提供512GB/s的速度,PCI-SIG公布PCIe7.0规范的0.3版本,预计要到2028年才会正式发布;与此同时,随着Intel支持PCIe 5.0的Ice Lake Xeon-SP CPU即将在今年底发布,再加上支持PCIe 5.0的AMD EPYC CPU和一众ARM CPU的逐渐出货,PCIe 5.0即将在2023年成为市场上的主流,其对应的Cable厂商做好准备,了解学习回顾下PCI-E的发展历程.

如图中的蓝色通道即为总线

常用的PCI总线带宽为133MB/S,于1992年诞生。接着因为在服务器领域传输要求于是Intel把总线位数提高到64,这样又出现了2种PCI总线,分别为64bit/33Mhz和64bit/66Mhz,带宽分别为266Mbps和533Mbps。稍后在显卡领域,Intel单独开发出了AGP,32bit,66Mhz,这样带宽为266Mbps,再加上后来AGP2.0的2X和4X标准,最高4X的带宽高达1Gbps,但是确切的说AGP不是真正的总线,因为AGP只能连接一个设备-显卡。

同时服务器领域,几家厂商联合制定了PCI-X,64bit133Mhz版本的PCI,带宽就为1Gbps,后来PCI-X 2.0,3.0又分别提升频率,经历过266Mhz,533Mhz,甚至1GMhz,这个带宽可以说是非常足够的了,不过这个时候PCI-X也面临一些问题:一方面是频率提高造成的并行信号串扰,另一方面是共享式总线造成的资源争用,总之也就是说虽然规格上去了,但实际效果可能跑不了这些指标。

于是,在2001年的英特尔春季IDF大会上,英特尔正式公布旨在取代PCI总线的第三代I/O技术,该规范由Intel 支持的AWG(Arapahoe Working Group)负责制定,并称之为第三代I/O总线技术(3rd Generation I/O,也就是3GIO),很明显英特尔的意思是它代表着下一代I/O接口标准。交由 PCI-SIG(PCI特殊兴趣组织)认证发布后才改名为“PCI-Express”。这个新标准将全面取代当时的PCI和AGP,最终实现总线标准的统一。它的主要优势就是数据传输速率高,目前最高可达到10GB/s以上,而且还有相当大的发展潜力。PCI Express也有多种规格,从PCI Express 1X到PCI Express 16X,能满足现在和将来一定时间内出现的低速设备和高速设备的需求。

PCI Express(以下简称PCI-E)采用了目前业内流行的点对点串行连接,比起PCI以及更早期的计算机总线的共享并行架构,每个设备都有自己的专用连 接,不需要向整个总线请求带宽,而且可以把数据传输率提高到一个很高的频率,达到PCI所不能提供的高带宽。相对于传统PCI总线在单一时间周期内只能实 现单向传输,PCI-E的双单工连接能提供更高的传输速率和质量,它们之间的差异跟半双工和全双工类似。

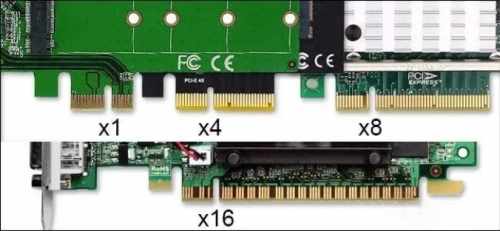

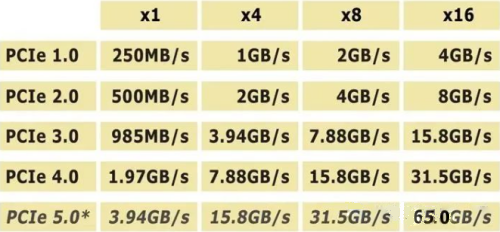

PCI-E的接口根据总线位宽不同而有所差异,包括X1、X4、X8以及X16,而X2模式将用于内部接口而非插槽模式。PCI-E规格从1条 通道连接到32条通道连接,有非常强的伸缩性,以满足不同系统设备对数据传输带宽不同的需求。此外,较短的PCI-E卡可以插入较长的PCI-E插槽中使 用,PCI-E接口还能够支持热拔插,这也是个不小的飞跃。PCI-E X1的250MB/秒传输速度已经可以满足主流声效芯片、网卡芯片和存储设 备对数据传输带宽的需求,但是远远无法满足图形芯片对数据传输带宽的需求。因此,用于取代AGP接口的PCI-E接口位宽为X16,能够提供8GB/s的带宽,远远超过AGP 8X的2.1GB/s的带宽。

常见的PCIE卡槽

尽管PCI-E技术规格允许实现X1(250MB/秒),X2,X4,X8,X12,X16和X32通道规格,但是依目前形式来看,PCI-E X1和PCI-E X16已成为PCI-E主流规格,同时很多芯片组厂商在南桥芯片当中添加对PCI-E X1的支持,在北桥芯片当中添加对PCI-E X16的支持。除去提供极高数据传输带宽之外,PCI-E因为采用串行数据包方式传递数据,所以PCI-E接口每个针脚可以获得比传统I/O标准更多的带 宽,这样就可以降低PCI-E设备生产成本和体积。另外,PCI-E也支持高阶电源管理,支持热插拔,支持数据同步传输,为优先传输数据进行带宽优化。

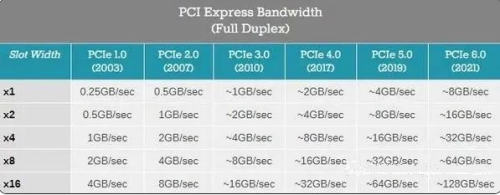

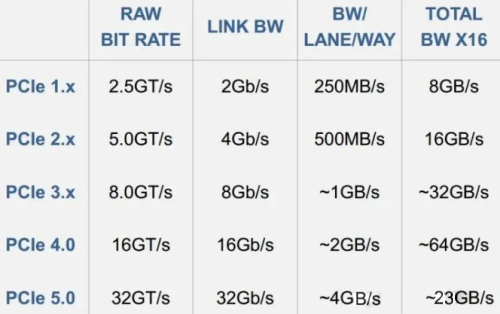

02 各个版本的PCI-E的规范如下

PCI-E 1.0规范:

PCI-E 1X(1.0标准)采用单向2.5G的波特率进行传输,由于每一字节为10位(1位起始位,8位数据位,1位结束位),所以传输速率为2.5G/10=250MB/S(250兆字节每秒),由此可以计算出来PCI-E 16X的单向传输速率为250MB/S*16=4GB/S,双向传输速率为8GB/S。

PCI-E 2.0规范:

PCI-E 1X(2.0标准)采用单向5G的波特率进行传输,由于每一字节为10位(1位起始位,8位数据位,1位结束位),所以单向传输速率为5G/10=500MB/S(500兆字节每秒),由此可以计算出来PCI-E 16X(2.0标准)的单向传输速率为500MB/S*16=8GB/S,双向传输速率为16GB/S,PCI-E 32X(2.0标准)的船速速率为32GB/S。

PCI-E 3.0规范:

PCI-E 1X(3.0标准)采用单向10G的波特率进行传输,由于每一字节为10位(1位起始位,8位数据位,1位结束位),所以单向传输速率为10G/10=1000MB /S(1000兆字节每秒),由此可以计算出来PCI-E 16X(3.0标准)的单向传输速率为1000MB/S*16=16GB/S,双向传输速率为32GB/S,PCI-E 32X(3.0标准)的双向传输速率高达64GB/S。

PCI-E 4.0规范:

PCI-E 4.0总线的速率是在PCI-E 3.0的基础上再翻一倍,单通道单向传输为16Gb/s,因此16通道双向传输的速率在理论上可以达到512Gb/s即64GB/s,另外PCI-E 4.0标准还会对PCI-E接口的存储设备例如PCI-E固态硬盘和PCI-E RAID卡等进行优化,尽可能发挥PCI-E总线的低延迟优势。另外PCI-SIG组织还透露,新的PCI-E标准将包含有外接式PCI-E的规范,他们将这个规范称之为PCI-E OCuLink,简单来说就是类似于英特尔主推的ThunderBolt接口。据称,PCI-E OCuLink基于PCI-E 3.0开发,将采用铜缆作为连接介质,可提供最低8Gb/s(PCI-E 3.0 x1)、最高32Gb/s(PCI-E 3.0 x4)的连接速率。

PCI-E 5.0规范:

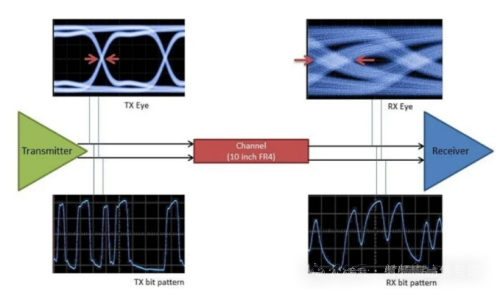

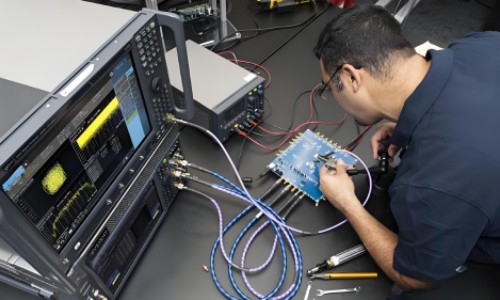

在PCIe 5.0将信号速率提升到32GT/s的时候,以太网设备的信号速率已经达到56Gbps,并正在向112Gbps迈进。从速率上来看,现有的测量设备应该能够完全满足PCIe 5.0信号的测试需求。但实际上PCIe 5.0是NRZ信号,56Gbps以太网信号是PAM4信号,PCIe 5.0信号的基频点反倒更高(16GHz vs 14GHz)

PCI-E 6.0规范:

PCIe 6.0 规范,达到 64 GT/s。近二十年来,PCI Express 技术一直是事实上的首选互连。PCIe 6.0 规范将 PCIe 5.0 规范 (32 GT/s) 的带宽和功率效率提高了一倍,同时提供低延迟和减少的带宽开销。

PCI-E 7.0规范:

最新一代 PCIe 7.0带宽翻了一番,在一条通道 (x1) 上单向实现 128GT / s 或 128Gbps 总吞吐量。综上所述,在 PCIe x16 插槽上,与独立显卡一样,双向总理论吞吐量为 512GB / s。同时,通常与 x4 PCIe 插槽配对的 NVMe SSD 可提供高达 64GB / s 的单向速度。最终规格将于 2025 年发布.

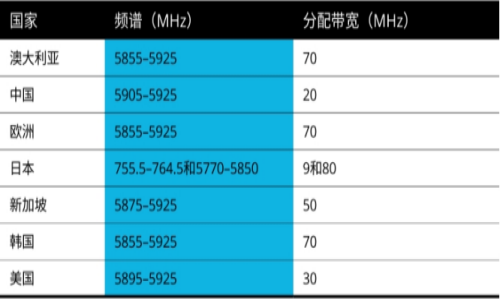

以下是目前发布的各标准及不同的位宽下速度的对比:

下表中详细展示了PCIe各版本各规格的单向带宽/速率。

大家可能都注意到,新版本带宽翻倍是PCIe的优良传统,需要PCIE5.0版本的协会技术规格,找客服CABLE009索取即可。

03 PCIe 5.0/6.0 布线将于2023年末推出

虽然 PCIe 7.0 正在开发中,但 PCIe 6.0 的第一个硬件仍在开发中,甚至 PCIe 5.0 设备也只有不到一年的时间。因此,在开发核心规范的同时,PCI-SIG 还在完成规范的一些辅助领域,特别是布线。预计将于今年第四季度发布。规格将涵盖 PCIe 5.0 和 PCIe 6.0(因为信号频率不变,PCIe 5.0的目的是简单地提高到PCIe 4.0标准的速度,而没有任何其他重要的新功能。例如,PCIe 5.0不支持PAM 4信号,只包括使PCIe标准能够在尽可能短的时间内支持32 GT/s所需的新功能),包括内部和外部电缆的规格。内部布线将把设备连接到系统内的其他部分——包括设备和主板/背板——而外部布线将用于系统到系统的连接。在信号技术和绝对信号速率方面,PCI Express 落后以太网一代左右。这意味着以太网工作组已经解决了高速铜信号的大部分初始开发问题。因此,尽管仍需努力使这些技术适用于 PCIe,但基本技术已经得到验证,这有助于稍微简化 PCIe 标准和布线的开发。

关注微博

关注微博 关注微信

关注微信 关注公众号

关注公众号 关注抖音号

关注抖音号