面向高信道衰减的低功耗发射机设计

面向高信道衰减的低功耗112 Gibit/s Duo-binaryPAM4 SerDes发射机设计

为了解决串行收发机在强信道衰减下误码过高的问题,采用 Duo-binary PAM4 编码技术设计了一款低功耗的112 Gibit/s SerDes 发射机。通过采用 Duo-binary PAM4 编码技术,解决了高速PAM4(Pulse Amplitude Modulation-4)信号衰减过大的问题;采用 CMOS 的1/4 速架构的4:1 合路器,降低了发射机的系统功耗;采用阻抗校准电路,提高了Duo-binary PAM4 发射机的线性度。该发射机采用CMOS 28 nm 工艺设计,0.9V电压供电。仿真结果表明:该发射机在20.9dB强信道衰减下,可以工作在112 Gibit/s,功耗为1.9 pJ/bit,且线性度达到88.3%。

近年来大数据产业蓬勃发展,飞速增长的数据量引发了对数据处理需求和传输需求的爆发式增长,传统的并行接口随着通信速度的不断提升,多条紧挨的通道之间会出现严重的串扰和耦合,严重影响信号质量。而高速串行接口( SerDes) 采用一对差分线进行信号传输,抗噪声、抗干扰能力强,因此串行接口逐步取代并行接口,节约了信道和 I/O 管脚,消除了同步问题,成为了主流高速接口。在数据率飞速发展中,传统的不归零码( Non Re-turn Zero,NRZ) 调制在 100 Gibit / s 以上的高速串口应用中信道衰减影响凸出,因此,四电平脉冲幅度调制串行接口逐渐取代NRZ,其奈奎斯特频率是NRZ的一半,较好地解决了数据在强信道衰减下误码过高的问题。

在这样的背景下,对高速 SerDes 进行深入研究。设计基于Duo-binary PAM4 编码技术的112 Gibit / s 的 Ser-Des 发射机,Duo-binary PAM4 编码其奈奎斯特频率更是PAM4 的一半,显著减少了面临的信道损耗。本文概括介绍了发射机总体电路架构,具体分析发射机的关键模块,并给出仿真验证结果。

1 发射机电路架构

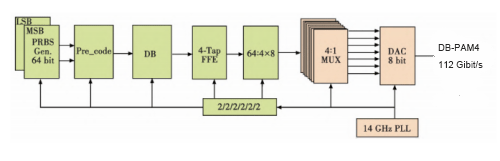

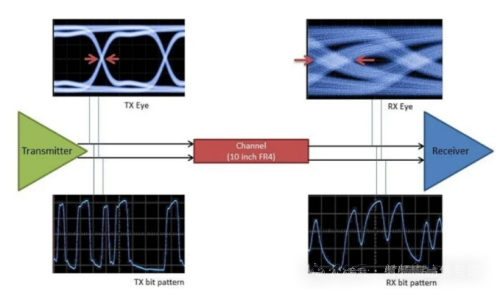

发射机是 SerDes 系统的数据发射端,用于将处理器、存储器或者传感器发出的多路并行数据串行化,并通过信道传输到接收机。实现高速数据的串行与均衡是发射机的主要任务。本文设计的发射机采用 DSP +DAC 架构,主要由预编码模块、DB( Duo-binary) 模块、64∶ 4 并串转换模块、1 /4 速率的四合一高速合路器、SST驱动电路组成,其系统框图见图 1。

图1 发射机系统框图

电路接收由伪随机码产生的64路875 Mibit/s 的并行信号,经过预编码模块来消除前后码元的相关性,后经过DB模块产生双二进制信号,64∶ 4并串转换模块将64路875 Mibit/s合成14Gibit/s 的高速串行信号,该模块所需的时钟由锁相环( Phase Locked Loop,PLL) 产生的14GHz时钟信号分频提供; 之后利用相位相差 90°的时钟产生输出脉冲,并将4路数据串化成1路高速的数据流,最后由驱动模块实现驱动,输出112 Gibit /s Duo-binary PAM4信号。

2 发射机电路设计

2.1 Duo-binary PAM4编码

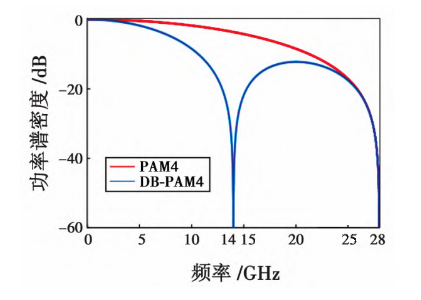

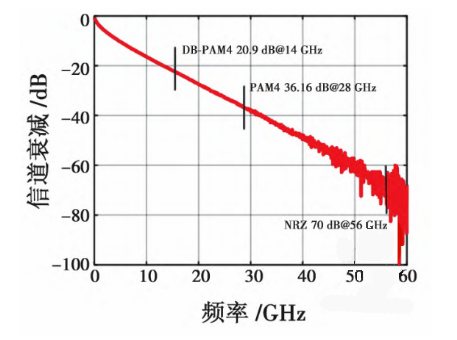

当前主流的调制方式为NRZ与PAM4调制,NRZ调制使用高低电平“0”和“1”传输信号,NRZ调制1UI 只能传输1 bit的“0”或“1”,而 PAM-4调制则采用4个电平“0”,“1”,“2”,“3”( 对应二进制编码为“00”,“01”,“10”,“11”) ,在 1UI 的时间内能传输2 bit的信息。相比于NRZ调制,PAM4实现了加倍的数据传输速率,并且在相同速率下,PAM4的奈奎斯特频率是NRZ的一半,使得信号遭受的信道损耗大幅减少。然而随着数据率的飞速发展,信道损耗问题越来越严重,制约了NRZ调制在 100 Gibit/s以上高速串口中的应用。在这种情况下,PAM4逐渐取代NRZ,其奈奎斯特频率是NRZ的一半,成为超高速串口的主流调制方式。而 Duo-binaryPAM4编码在PAM4的基础上,其奈奎斯特频率更是PAM4 的一半,如图 2 所示( 112Gibit/s Duo-binary PAM4信号的奈奎斯特频率为14GHz,而 PAM4 信号为 28GHz,NRZ 信号为56 GHz) ,这带来了以下好处: 1) 使得信号遭受的信道损耗大幅减少,56Gibit/s NRZ 信号在奈奎斯特频率处的损耗高达 70 dB,PAM4 信号降低为36.16dB,而DB-PAM4信号降低到了20.9dB,如图 3 所示; 2)信号接收端采用同样的采样率可以获得更多的采样点,数据精度提高。

图2 功率谱密度

图3 信道损耗

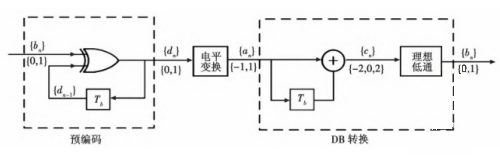

图 4 所示为NRZ信号转换成DB信号的线性模型。将两个相邻不相关的码元变成相关的三电平DB信号。DB 信号进行传输时会出现差错传递,因此,在进行双二进制转换前加入预编码电路来消除前后码元的相关性。

图4 线性模型

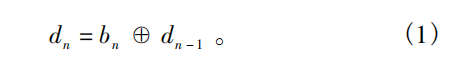

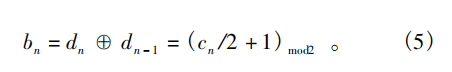

预编码实现模二相加运算,将输入的二进制序列{bn} 预编码成为序列{dn} ,即

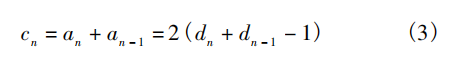

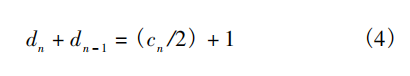

电平转换将经过预编码的{dn}序列由单极性{0,1} 转化为双极性码{an} 序列{-1,1},实现功能

通过延时相加电路生产DB序列{cn}

化简得

由式(1)和式(4)将输入序列{bn}表示为

2.2 1/4 速架构的4∶1 MUX设计

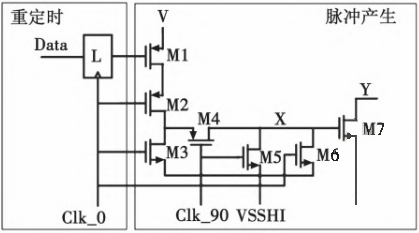

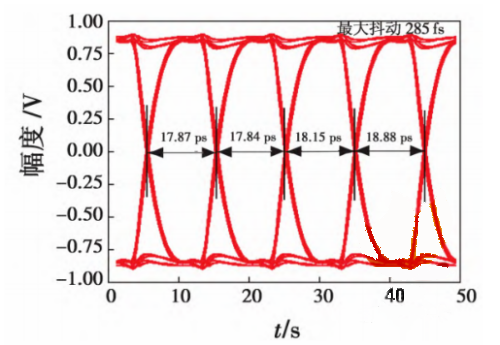

高速的合路器设计是SerDes 发射机设计的关键,合路器必须要提供充足的时序裕度以保证时序的正确性。传统的1/2 速架构合路器留给数据建立和保持的时间只有1UI,当数据率达到100Gibit/s 时,1UI仅为10ps,为了扩展时序裕度,设计了基于4∶ 1合路器的1/4速架构,合路器的结构如图5所示。其时钟频率是输出频率56Gibit/s的1/4即14GHz。每个脉冲产生单元在2 个相差 90°相位且周期是 4UI 宽度周期的时钟驱动下产生 1UI 的数据输出脉冲。这4个相同的脉冲产生单元然后在流水线时钟的驱动下将4路数据串行化成 1 路高速的数据流输出。

图 5 合路器架构

图 6 给出了4∶1 MUX 的仿真输出眼图。从仿真结果可以看出,该结构的输出眼宽大约是17.8ps,且4只眼睛均匀,最大抖动为225fs。

图 6 仿真眼图

2.3 驱动电路设计

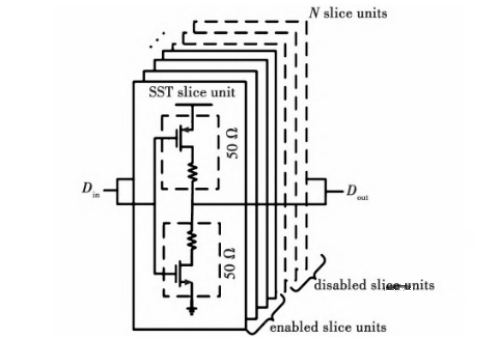

驱动器有两种基本结构,即电流模驱动(Current-Mode Logic,CML) 和电压模驱动(Source-Series Termi-nated,SST) 。在输出相同摆幅时,电压模驱动所需的电流仅为电流模驱动的1/4。在高速情况下,电压模式驱动器比电流模式驱动器更快,线性度更好,并提供更好的垂直和水平眼开口,因此,本文采用SST驱动电路实现112 Gibit/s DB-PAM4。SST电路的输出阻抗由串联电阻和反相器输出阻抗决定。每条支路并联输出阻抗设定为50Ω,以实现阻抗匹配。

为了实现SST驱动的输出阻抗的校准,本文采用结构如图7所示的输出阻抗校准电路。

图 7 阻抗校准的电压模驱动

该电路将传统的SST驱动电路分成N个相同、并联连接的子单元,其中K个子单元是导通的(K<N) ,导通单元的总输出阻抗等于传输信道的阻抗。当输出阻抗大于传输信道的特征阻抗时,增多K的数量,即导通关断的子单元; 反之,减少K的数量。这样的校准电路不仅可以有效调节输出阻抗,并且不消耗电压裕度。

3 发射机整体仿真验证

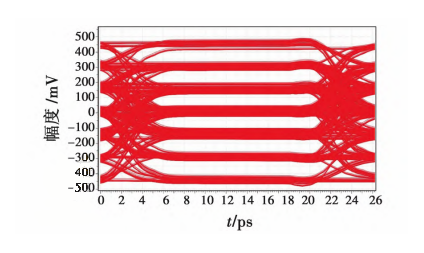

本文发射机是基于 CMOS 28nm工艺进行设计的。设计验证时,采用伪随机码作为并行输入数据,采用锁相环(PLL) 产生14GHz的时钟作为原输入信号并进行的分频处理给各模块提供对应的时钟,进行仿真验证得到发射机的眼图,如图 8 所示。

图8 发射机仿真眼图

其中,6只眼睛垂直张开高度从上而下依次为80.78mV,82.44mV,84.12mV,79.27mV,88.65mV,86.78mV;水平张开宽度依次为14.86ps,13.76ps,13.86ps,14.64ps,13.96ps,15.63ps;6 只眼睛垂直张开高度比例为1: 1.02:1.04:0.98:1.09:1.07。6 只眼睛最小的垂直张开高度为79.27 mV;最小的水平张开宽度为13.76ps,约为0.7UI。可以看出本文设计的发射机电路性能良好,满足设计要求。

4 结论

本文基于CMOS 28nm工艺,设计了一款数据率为112 Gibit/s的Duo-binary PAM4发射机。1/4速架构的 4∶ 1MUX模块采用CML结构,驱动电路采用输出阻抗可调整的电压模驱动,采用64bit的伪随机码作为输入数据,建立仿真测试环境。仿真测试结果表明,当发射机工作在112Gibit/s时,MUX 电路功能正确,设计的发射机能工作于设计的速率,符合设计要求。

从与其他发射机性能的对比结果可以看出,本文设计的发射机与先进的10nm工艺设计相比,眼高有着更好的性能,与相近的40nm工艺比,也有着功耗低的优势。

来源:电光与控制

关注微博

关注微博 关注微信

关注微信 关注公众号

关注公众号 关注抖音号

关注抖音号