天华中威科技微波小课堂_RFSOC关键配置之RF-ADC内部解析

RF-ADC简介

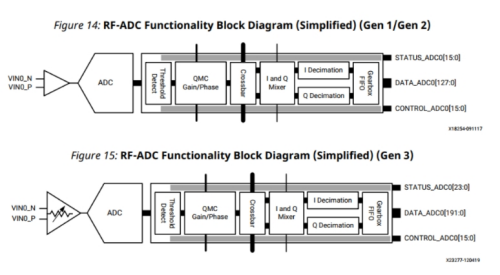

tile 中的每个 RF-ADC 都有自己专用的高性能输入缓冲器,包括针对直接 RF 应用优化的功能,包括正交调制器校正 (QMC),全复杂混频器和抽取滤波器。前两代和第三代在结构上基本相同。

某些功能只能在一个 Tile 中的 RF-ADC 配对时执行。偶数 RF-ADC 用于 I 数据路径,奇数 RF-ADC 用于 Q 数据路径。一个 Tile 的所有可用内置功能以及一个 Tile 中的每个 RF-ADC 都使用支持 RFdc 驱动程序 API 或 Vivado IDE 中的内核配置界面进行配置。

RF-ADC 模拟输入

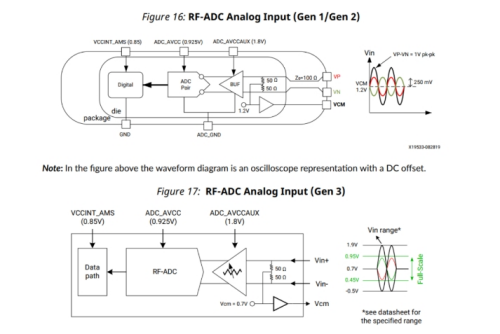

Tile 中的每个 RF-ADC 都有自己的差分模拟输入缓冲器。该输入针对性能进行了优化,并且需要源阻抗匹配以获得最佳动态性能。

Gen 1/Gen 2 和 Gen 3 之间的 Vcm 不同。

有几种方法可以驱动一个Tile 中的 RF-ADC。驱动 RF-ADC 可以是有源的也可以是无源的。但是,通过差分驱动模拟输入可以实现最佳性能。对于交流耦合模式,输入信号应使用电容器进行交流耦合。对于 DC 耦合模式,输出 VCM 缓冲器启用,如上图所示。该缓冲器仅在选择直流耦合模式时启用。此 VCM 缓冲器允许您根据 ADC 内部通用要求设置外部有源驱动电路的共模。每个图块有两个 VCM 缓冲器(VCM01、VCM23)。

当处于直流耦合模式并使用外部有源器件驱动时,如果 Zynq UltraScale+ RFSoC 尚未上电,确保驱动电路将共模电平拉至地非常重要。当 Zynq UltraScale+ RFSoC 上电时,共模电平应在指定范围内。这里假设驱动电路和 RFSoC 具有符合 Xilinx RFSoC PCB 集成指南的公共接地层。

对于以信噪比 (SNR) 为关键参数的所有应用,赛灵思建议使用差分变压器或巴伦配置。

对于未使用或禁用的 ADC 通道,以下是有关输入引脚的建议:

当 IP 中未启用 ADC 通道并且该通道永远不会使用时,应将 ADC VIN 引脚连接到直接接地。

当一个 ADC 通道在 IP 中启用但没有被 PCB 上的任何东西驱动时,RF 输入可能会悬空。您必须确保选择了交流耦合模式。这对于某些 SYSREF 分配用例可能是必需的,其中 ADC 通道可以通过软件上电或断电,同时在 IP 中启用该通道。

Digital Step Attenuator (Gen 3) (数字步进衰减器、第 3 代)

在某些情况下,模拟输入信号幅度/功率可能会有很大差异,例如,由于不同的 RX 信号强度或存在阻塞/干扰信号。这种可变信号电平传统上是使用可变增益放大器 (VGA)/数字步进衰减器 (DSA) 在外部处理的,它可以调整幅度以获得最佳输入范围。

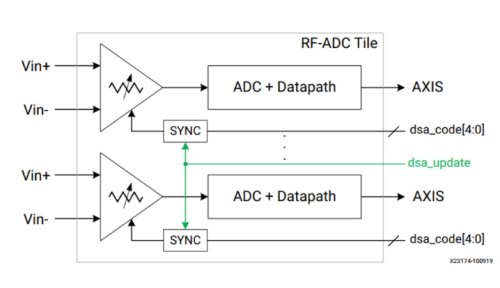

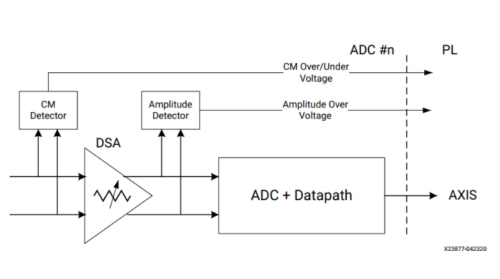

DSA 与缓冲器集成在一起,如下图所示。

DSA 关键参数(第 3 代)

有关 DSA 参数,请参阅 Zynq UltraScale+ RFSoC 数据表(DS926)。

DSA 操作细节(第 3 代)

片上 DSA 支持以下两种行为:

用户使用直接可编程逻辑输入选择衰减值。

在过压事件中强制或禁用自动衰减值(连同缓冲器)。

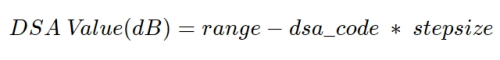

来自 PL 的 5 位实时信号 (dsa_code) 根据以下公式直接设置 DSA 值。

DSA_code 的范围是从 0 到最大允许代码,该代码映射到从最大衰减值到 0 dB 的 DSA 值,步长和范围在 Zynq UltraScale+ RFSoC 数据表中定义(DS926);其他 dsa_code 值无效。例如,假设 DSA 的范围为 27 dB,步长为 1 dB,如果您希望 DSA 值为 10 dB,则 dsa_code 值为 17 (27 - 10),dsa_code 为 0b10001。

dsa_code 使用触发信号 (dsa_update) 的上升沿进行更新。一旦被 s_axi_aclk 捕获,触发信号是异步的,这允许最快的操作,并且它被分配到一个 tile 内的所有通道,以允许同时更新 DSA 代码。

从 dsa_update 断言到数字输出处代码更改的传播延迟对于双 RF-ADC 和四 RF-ADC 分别约为 400 T1 和 220 T1。

确切的更新时刻取决于模拟电路内触发器的本地同步;因此,实际更新时间存在一些不确定的采样时钟。还有一些 RFdc API 可用于设置和获取以 dB 为单位的 DSA 值。API 独立更新每个通道,响应时间比实时端口更新慢。

过压(第 3 代)

在 RF-ADC 模拟输入缓冲器模块内检测到过压情况,并使用标志进行通信。当检测到这些条件时,模拟模块也会保护输入。这种保护是自动的,不需要数字电路的任何配置或交互。处理两种类型的过电压:

Over Amplitude(过振幅):这是缓冲器输出振幅对于 RF-ADC 内核来说太大的情况,它在单端缓冲器输出上被检测到。当检测到过幅情况时,中断机制和过电压实时输出信号都会对其进行标记。

Outside Common-Mode range(共模范围外):这是输入端的共模超出/低于可靠范围的地方。当检测到共模欠压或过压情况时,中断机制和 cm_over_voltage 或 cm_under_voltage 实时输出信号都会对其进行标记。

下图显示了检测到上述两个输入违规的位置:

Over Amplitude (Gen 3)

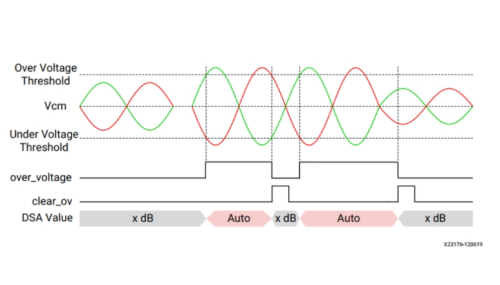

当一个 Over Amplitude 发生时,片上 DSA 被自动设置。在此期间,输入缓冲器保持活动状态,衰减数据被发送到数字电路,并且“粘性”过电压输出信号被断言并保持断言,直到您将其清除。

要清除 over_voltage 信号,请置位 clear_ov 信号,它是一个异步的上升沿敏感输入,置位后,将 DSA 设置返回到先前编程的用户值。

上图显示了在存在大信号时设置的幅度过电压。

输出信号 over_voltage 被置位,并保持设置直到您将其清除,而进入 RF-ADC 的信号会自动衰减(自动)。它还显示了如果在大信号持续存在时清除事件会导致 over_voltage 信号重新生效,并且衰减会继续自动设置。

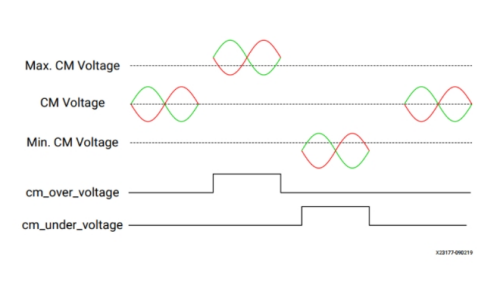

超出共模范围(第 3 代)

当超出共模范围时,输入缓冲器被有效禁用并自动保护。

如果检测到低于或高于共模信号,则将电平标志 cm_under_voltage 或 cm_over_voltage 发送到 PL。由于 RF-ADC 在此事件期间被禁用,因此数字数据路径中的数据被门控为 0。上电过程的校准阶段将不会开始,直到共模处于安全工作范围内。

cm_under_voltage 或 cm_over_voltage 信号在共模超出阈值时保持设置,并在共模返回安全工作范围时自动取消断言。如下图所示:

作者:Vuko-wxh

关注微博

关注微博 关注微信

关注微信 关注公众号

关注公众号 关注抖音号

关注抖音号