天华中威科技微波小课堂_锁相环的杂散怎么优化

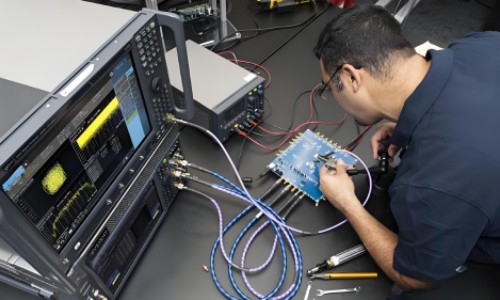

锁相环噪声分为随机噪声和确定性噪声,从频率上来说就是随机杂散和确定性杂散。

杂散的存在会恶化相位噪声,影响邻道,影响SNR,从而影响整个系统的通信质量。

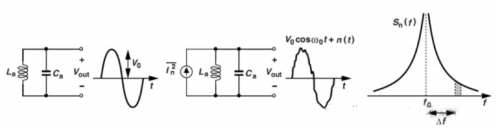

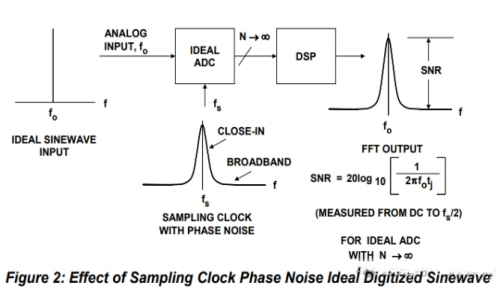

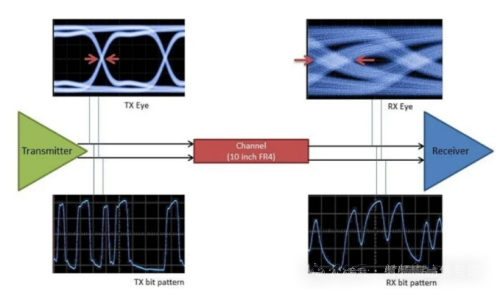

随机噪声主要来源于器件的热噪声和闪烁噪声. 在频域上表现为频线的裙带( phase noise) , 在时域上表现为随机的抖动( jitter)。

确定性噪声主要来源于振荡器外部周期性干扰信号, 在频域上表现为不需要的 杂散( spur) , 在时域上则表现为周期性的抖动( 抖动的幅度呈现周期性) 。

在锁相环设计中, 随机噪声通常由振荡器的品质因子( Q 值) 、偏置电路的噪声和控制环路共同决定。

而确定性噪声却来源很多, 常常无法通过仿真发现, 这使得杂散常常成为锁相环设计失败的主要原因。

优化锁相环的杂散是设计锁相环的关键之一。

了解到锁相环的杂散成因就可以针对性的进行杂散优化。

1.电源pushing

电压控制振荡器将来自鉴相器的误差电压转换成输出频率。器 件“增益”定义为KVCO,通常以MHz/V表示。电压控制可变电容 二极管(变容二极管)常用于调节VCO内的频率。VCO的增益 通常足以提供充分的频率覆盖范围,但仍不足以降低相位噪 声,因为任何变容二极管噪声都会被放大KVCO倍,进而增加输出相位噪声。

电源波动也会给输出频率变化带来干扰成分。VCO对电源波动的灵敏度定义为VCO推压(Kpushing),通常是所需KVCO的一小部分。例 如,Kpushing通常是KVCO的5%至20%。因此,对于高增益VCO, 推压效应增大,VCO电源的噪声贡献就更加举足轻重。

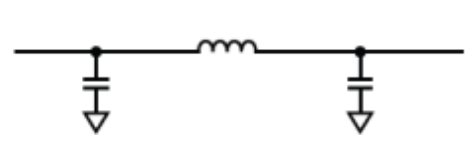

所以锁相环的电源通常都采用低噪声的LDO。为了进一步抑制LDO的噪声通常会在LDO后加滤波器。简单的LC π 滤波器通常足以将带外LDO噪声降低20 dB。

2.参考杂散

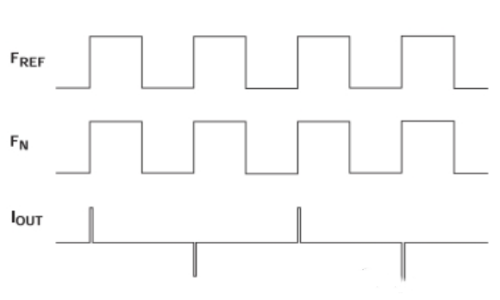

当PLL锁定时,PFD的相位和频率输出(fREF和f N)理论上是相等的,但实际设计的电路时不是完全相等,只是小于一定的范围认为其相等,此时PFD处于锁定状态。

尽管这些脉冲具有极窄的宽度,但它们的存在意味着驱动 VCO的直流电压是由频率为f REF的信号进行调制的。这会在 RF输出中产生参考杂散,且发生的失调频率为f REF的整数倍数,即我们常说的整数边界杂散。

如何优化整数边界杂散

常见的方法有三种:

● 改变鉴相器频率,使得目标频率偏移整数边界杂散。在输入端加入预分频器就是这个道理。

● 降低环路带宽,使得整数边界杂散落入环路带宽之外,从而被衰减。

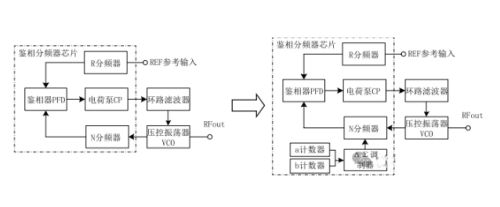

● 整数边界的杂散是由于周期性的时间选择同样的分频导致的,可以通过算法让该周期随机性,同时可以产生小数分频。

3.小数杂散

小数分频实现的过程,如果是周期性的N分频和N+1分 频,那么这个周期性的信号必然产生一杂散信号调制在输 出频率上。该杂散信号与ΔΣ调制的调制方式直接相关。

小数模式虽然在宏观上看实现了小数分频。但是从单个周期看,其实锁相环一直处于失锁重新锁定的过程, 所以小数模式下输出频率的相位一直在变化,且锁相环 处于动态锁定过程中,电荷泵上下偏电流一直处于工作状态。

如何优化小数杂散

现有小数杂散优化的技术有:

● 加大环路滤波抑制能力,部分杂散幅度降低;注意:环路变窄,阶数变高,电路负载,锁定时间加长。

● 修改鉴相频率,规避部分杂散点;

● 减小泵电流,降低充放电效果,优化杂散幅度;

● 更改新品内部电荷泵设计;

总结:锁相环的杂散通常是系统杂散产生的大头,优化锁相环杂散可以系统的性能。

关注微博

关注微博 关注微信

关注微信 关注公众号

关注公众号 关注抖音号

关注抖音号