天华中威科技微波小课堂_SDR实战-RFSOC架构

高层次结构

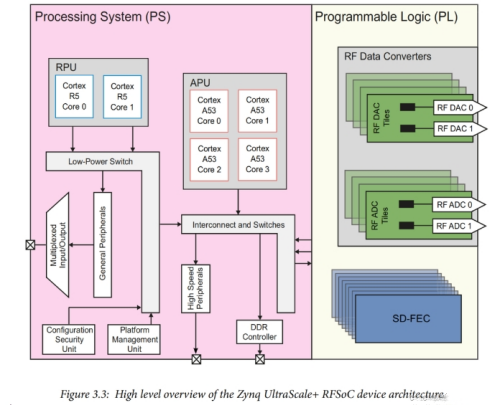

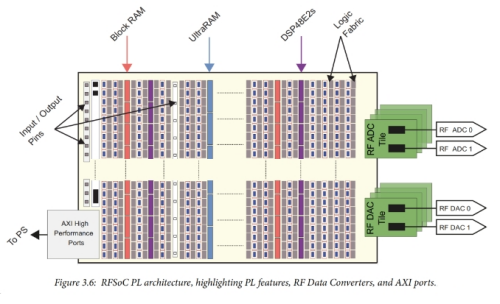

和传统的ZYNQ的组成一样,RFSOC也是由PL和PS组成。

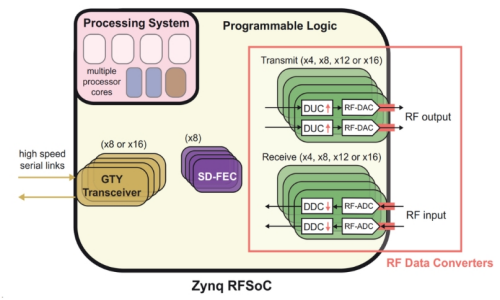

其中下图中的红框内的RF相关的部分是硬化的,而并不是可编程逻辑,但却具有可编程性。

RFSOC的高层次结构图

● RF Data Converter (RFDC) blocks:集成了ADC和DAC,可以在Gsps的高采样率下工作,使其可以直接采样许多radio signals。还包含可编程数字上变频器DUCs(Digital Upconverters)和数字下变频器DDCs(Digital Downconverters),用于在baseband(接近0Hz信号)和modulated frequencies之间进行转换。

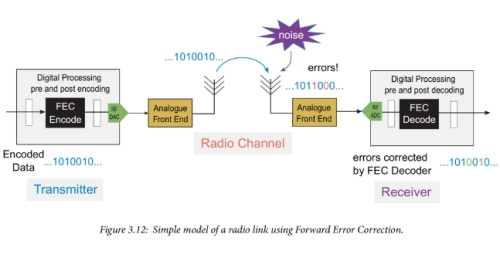

● Soft Decision Forward Error Correction (SD-FEC) blocks:软判决前向纠错模块:无线通信方案通常采用某种形式的前向纠错(FEC)编码来减轻无线电信道引入的错误(即可让接收器检测到比特错误,并在可能的情况下进行纠正)。

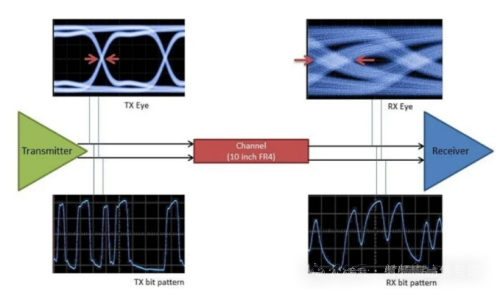

● Gigabit Transceivers (GTY Transceivers):RF SoC可以用于实现无线电前端,但需要高速链路连接到核心网络,这些通常以有线或光的形式实现。RF SoC上支持所需的接口,由经过加固的GTY收发器块、高速率串行接口提供,可以实现许多不同的标准。

● Programmable Logic(PL):可编程硬件资源,用于实现自定义无线电架构。

● Processing System(PS):包括一个四核应用处理单元(APU)、一个双核实时处理单元(RPU),以及平台管理(PMU)和安全功能。还有本地内存、互连和外围接口。

处理器系统-PS

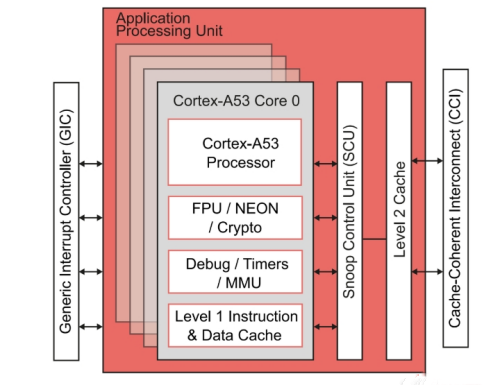

应用处理单元-APU

APU:Application Processing Unit。

包含一个四核 Arm Cortex-A53 处理器,它拥有四个处理核心,每个核心都有自己的专用计算单元。

每个核都包括一个浮点单元(FPU)、Neon 媒体处理引擎(MPE)、加密扩展(Crypto)、内存管理单元(MMU)和每个核心的专用一级缓存。

整个 APU 都可以访问一个 Snoop 控制单元(SCU)和二级缓存。

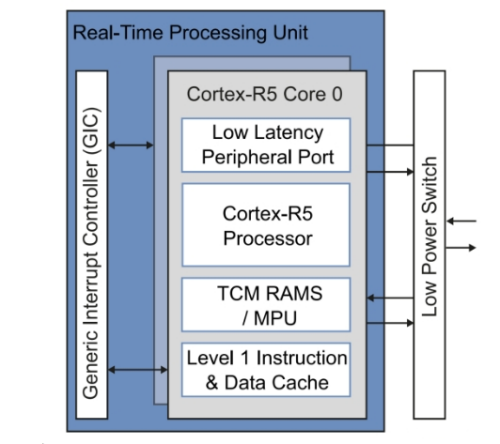

实时处理单元-RPU

RPU:Real-Time Processing Unit

包含两个用于实时应用和确定性系统控制的Arm Cortex-R5内核,并具有低延迟性能。

RPU包含多个计算单元和存储器,包括一个浮点单元、紧耦合存储器(TCM)、两个本地高速缓存和一个存储器保护单元(MPU)。

平台管理单元-PMU

PMU:Platform Management Unit

PMU 包含一组三个经过硬化处理的 MicroBlaze 处理单元。

MicroBlaze CPU 通过多数表决系统进行配置,以增加关键平台管理功能的可靠性。

PMU 包含多个存储器以及能够有效管理 RFSoC 设备的固件。

配置安全单元-SCU

SCU:Configuration Security Unit

RFSoC设备的安全性由配置安全单元(CSU)处理,该单元包括一个安全处理器块(SPB)和加密接口块(CIB)。

与PMU类似,SPB包含三个MicroBlaze处理单元。

这些处理单元管理Arm处理器的安全启动以及几个其他安全特性,例如物理不可克隆函数(PUFs)和防篡改保护。

可编程逻辑-PL

RFSoC设备上可用的PL相当于FPGA。PL是SDR设计的一个组成部分,因为它直接与RF-ADCs和RF-DACs的接口相连。

射频数据转换器-RFDC

PL与RF的接口

RFSoC PL 充当 RF-ADC 和 RF-DAC 通道的网关。

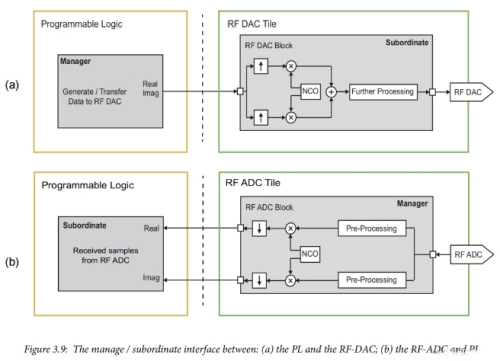

信号数据在 PL 和 RFDC 之间使用 AXI4-Stream 接口进行传输。

AXI4-Stream 接口特性包括一个数据源(称为主设备 /管理器)和一个数据接收器(从设备 / 下属)。

首先,对于 RF-DAC 通道,我们可以看到 PL 负责将数据传输到 RF 接口。在此设置中,PL 是管理器,RF-DAC 是下属,如图 3.9(a) 所示。在这里,显示的是复数到实数配置,因为 RF-DAC 通道中的复数数据变成了模拟实数数据。

相比之下,RF-ADC 通道将数据传输到 RF 接口供 PL 使用。在这种情况下,RF-ADC 是管理器,PL 是下属。此设置的示例如图 3.9(b) 所示,这是一个复数到复数配置的示例。

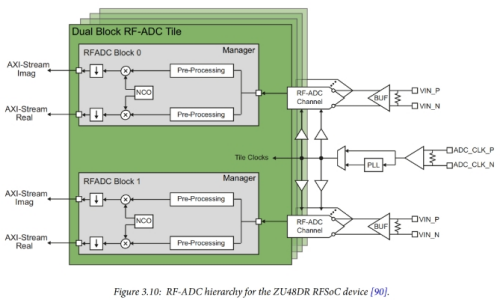

RF-ADC层次结构

RF-ADC 可以配置为三种不同类型中的任意一种,每种类型针对任何给定设备都是固定的。RF-ADC 可以配置为每Tile 4 个块、每Tile 2 个块或每Tile 1 个块(分别称为四重、双重和单重块)。例如,下述的 ZU48DR 使用每Tile 2 个块的布局(即双重块),这意味着总共需要 4 个Tiles来容纳所有 8 个 RF-ADC 块。

每个Tile都包含一个锁相环(PLL),用于生成芯片内部所需的时钟。PLL需要一个外部低抖动的片外时钟才能有效工作。

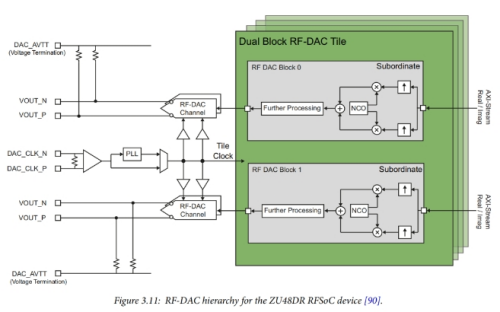

RF-DAC层次结构

与RF-ADC类似,可以配置为每Tile2个块或4个块,每个Tile都有一个PLL。

前向纠错-SD-FEC

在发送端,FEC编码器用于在调制和传输之前的源数据上,提高了链路的质量。

在接收端,FEC解码器可以检测和纠正发生的任何错误(上限取决于编码方案)。

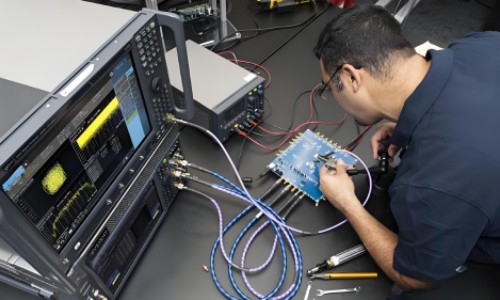

设计方法 Design Methods

那么一般的RFSOC设计方法有哪些呢?

同样的,根据RFSOC的结构类似,设计也分为硬件部分和软件部分。

PL端:Vivado IDE,还有集成在MATLAB和Simulink环境中的block-based tools、Vitis™Model Composerand HDL Coder;

PS端:PYNQ framework。这是AMD的一个开源项目,有助于在AMD自适应计算平台上实现软件和硬件的集成和生产力。它通过将SoC硬件设计、Linux和Python的元素与Jupyter环境相结合来实现这一点,用于应用程序开发。

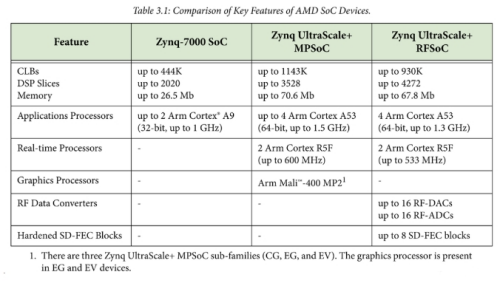

ZYNQ家族对比

需要注意的是ZYNQ-7000中的ARM处理器是32bit,而其他的为64bit。

关注微博

关注微博 关注微信

关注微信 关注公众号

关注公众号 关注抖音号

关注抖音号