[行业动态]英特尔最新FinFET制程是其代工战略中的关键

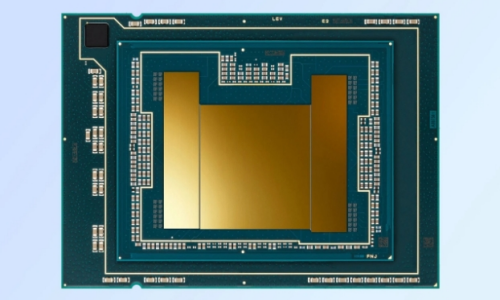

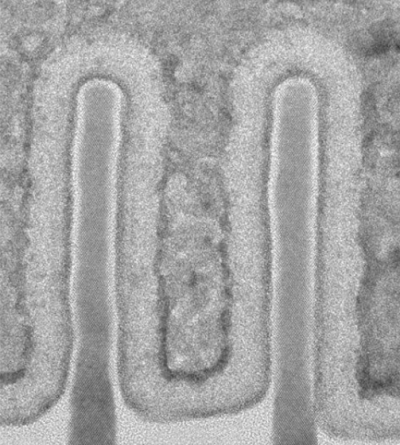

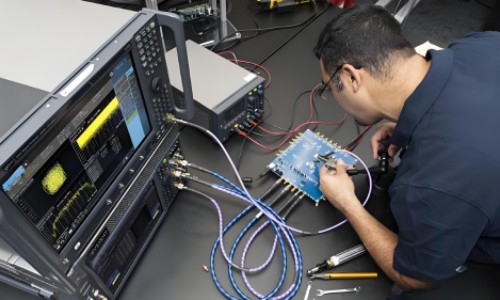

在最近的超大规模集成电路(VLSI,VLSI Symposium)研讨会上,英特尔详细介绍了其最新的“Intel 3”制造工艺。与之前的“英特尔 4”工艺相比,Intel 3-PT工艺在相同功耗下性能提升了 18%。虽然 FinFET(鳍式场效应晶体管)技术自 2011 年推出以来已被广泛采用,最后一代使用 FinFET 结构的产品,标志着向更先进技术的过渡。此外,这项技术对该公司成为代工厂并为其他公司生产高性能芯片的计划至关重要。

Intel 3工艺的重要特征之一是引入了偶极功函数金属(DFM),它允许芯片设计人员选择不同阈值电压的晶体管。阈值电压(VT_TT)决定了晶体管开启或关闭的水平,对于芯片的整体性能至关重要。工艺可以在单个芯片上实现四种不同阈值电压的晶体管,从而优化不同功能模块的性能。例如,缓存存储器通常需要高阈值电压以减少电流泄漏,而其他电路可能需要低阈值电压以实现更快的开关速度。

阈值电压由晶体管的栅极堆叠、控制晶体管电流的金属层和绝缘层设置

从历史上看,“金属的厚度决定了阈值电压,”英特尔负责铸造技术开发的副总裁Walid Hafez解释道,“功函数金属越厚,阈值电压就越低。”但随着器件和电路的规模缩小,这种对晶体管几何形状的依赖也带来了一些缺点。

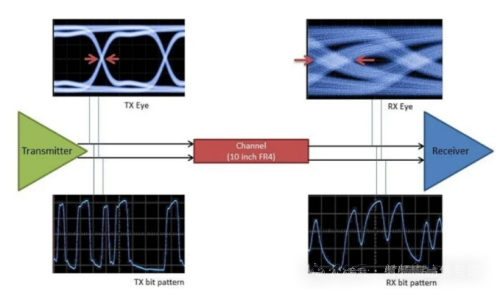

制造过程中的小偏差会改变栅极中金属的体积,导致阈值电压的范围有些宽。这就是Intel 3工艺从只为自己生产芯片到作为代工生产芯片的转变。

Hafez表示,“外部代工厂的运营方式与英特尔等集成设备制造商的运营方式非常不同。” 铸造客户“需要不同的东西……他们需要的东西之一是阈值电压的变化非常小。”英特尔不同;即使没有严格的阈值电压容差,它也可以通过将性能最好的部件转向数据中心业务,而将性能较低的部件转向其他细分市场来销售所有部件。

“很多外部客户不这么做,”他说,“如果一个芯片不符合他们的限制,他们可能不得不放弃它。所以,Intel 3要想在代工领域取得成功,就必须有非常严格的变化。”

工艺的关键创新

偶极功函数材料保证了对阈值电压的必要控制,而不必担心栅极中有多少空间。传统上,金属厚度越大,阈值电压越低。然而,随着工艺节点的缩小,这种方法的精度受到了挑战,制造过程中的微小偏差可能导致较宽的阈值电压范围。

在Intel 3-PT工艺中,偶极功函数材料确保了对阈值电压的精确控制,从而满足外部代工客户对芯片一致性和可靠性的需求。这一创新使英特尔在代工市场更具竞争力,与台积电和三星等领先代工厂形成了差异化。这种结构的确切成分是什么是商业秘密,但镧是早期研究中的一种成分,也是比利时微电子研究中心Imec提出的其他研究中的关键成分。这项研究关注的是如何最好地围绕水平硅带堆叠而不是一两个垂直鳍构建材料。

INTEL

在这些被称为纳米片或栅极全能晶体管的器件中,每个硅带之间只有纳米,因此偶极子是必要的。三星已经推出了一种纳米片工艺,英特尔的20A工艺计划在今年晚些时候推出。Hafez说,在Intel3中引入偶极功函数有助于使20A及其继任者18A进入更成熟的状态。

Intel 3的工艺

偶极功函数并不是Intel 3比前代产品提高18%的唯一技术。Intel 3工艺还包括多项技术改进:更完美的鳍片,提高了晶体管的电特性一致性;更清晰的晶体管接触,减少了接触电阻;以及更低的互连电阻和电容,提升了整体电路的性能和效率。这些技术改进共同推动了英特尔 3 工艺相较于前代产品性能提升 18%。(Hafez在这里详细介绍了这一切:

https://community.intel.com/t5/Blogs/Intel-Foundry/Intel-Foundry/Intel-Delivers-Leading-Edge-Foundry-Node-with-Intel-3-Technology/post/1607454。

英特尔计划使用Intel 3-PT工艺制造其新一代Xeon 6 CPU。这种工艺将推出三种技术变体,包括3-PT版本,该版本采用9微米硅通孔(TSV),用于3D堆叠技术。英特尔预计英特尔3-PT将成为其代工工艺的核心,持续为高性能芯片制造提供支持。Hafez表示:“我们预计Intel 3-PT将在未来一段时间内成为我们铸造工艺的支柱。”

文章来源:IEEE电气电子工程师学会

关注微博

关注微博 关注微信

关注微信 关注公众号

关注公众号 关注抖音号

关注抖音号